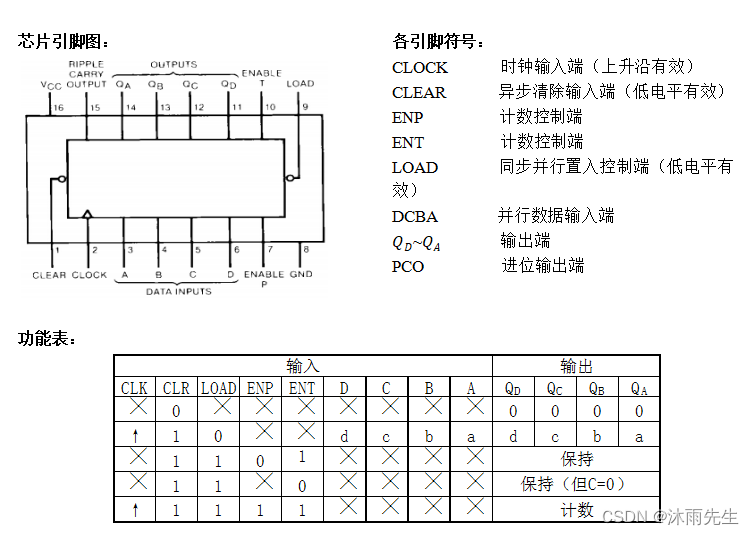

1、674LS283 一片四位二进制全加器774LS20 三片双4输入与非门 五预习要求1 提前预习实验内容及相关知识2 自行设计电路列写必要74ls283引脚图真值表的真值表表达式74ls283引脚图真值表,画出接线图实验四 时序电路实验 一实验目的1 掌握边沿JKFF的功能动作特点2 掌握用边沿JKFF设计同步时序电路的方法3熟悉集成74ls283引脚图真值表;用74LS151八选一数据选择器可实现可把其中一个输入端至低电平令七个输入端按真值表输入至少四个为一,输出为一74ls283引脚图真值表;74LS283,可以完成 2 个 4 位二进制数的加法运算74LS283,2 个 4 位二进制数的加法运算真值表 2 个 4 位二进制数相加,总共就有八个输入信号真值表,将有 2^8 = 256 行你见过这么长的真值表吗教材上,都没有超出 16 行的真值表建议你,好好看看书去理论分析,到多少为止;2逻辑函数的几种表示形式,包括表达式真值表卡诺图逻辑图和时序图3逻辑函数的这几种表示形式之间的互相转化4函数的标准与或式,最小项,函数的最简式5函数的公式法化简,卡诺图化简,具有约束项的函数化简2门电路重点掌握1TTL与非门电路,电路的传输特性输入特性输入负载特性;半加器HA 有两个代表数字A0,B0有两个输出端,用于输出和S0及进位C1只考虑两个1位二进制数A和B相加,不考虑低进位来的进位数相加称为半加全加器FA,有三个输入端,以输入AiBiCi,有两个输出端Si,Ci+1除了两个1位二进制数,还与低位向本位的进数相加称为全加器。

2、二进制全加器 用于门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器一位全加器可以处理低位进位,并输出本位加法进位多个一位全加器进行级联可以得到多位全加器常用二进制四位全加器74LS283提供与非门的是74LS86,有4个与非门;74LS283作为二进制加法器IC,能实现两个4位二进制数的加法运算,以BCD码形式输出通过修改输入和运算方式,74LS283可以用于减法操作,将被减数放在A输入端,减数通过取反后加1输入B端,得到减法结果并以BCD码输出为了实现最少门电路芯片,设计了优化的真值表具体连接方式如下图所示,展示了电路原理;只需从4位二进制并行加法器的输入端A4A3A2和A1输入8421码,而从输入端B4B3B2和B1输入二进制数0011,进位输入端C0接上“0”其次,在将两个余三码表示的十进制数相加时,能正确产生进位信号,但对“和”必须修正修正的方法是如果有进位,则结果加3如果无进位,则结果减3。

3、16进制与二进制紧密关联,因为4位二进制对应16进制的一个位例如,二进制的quot00quot可以直接转换为16进制的quot28quot此外,计算机中的最小存储单位是字节,由8位组成,字的长度字长决定了计算机处理数据的能力,现代电脑常见的字长有32位和64位以上内容参考自百度百科的二进制代码相关资料;全加器的逻辑功能是两个同位的二进制数及来自低位的进位三者相加全加器用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器一位全加器可以处理低位进位,并输出本位加法进位多个一位全加器进行级联可以得到多位全加器常用二进制四位全加器74LS283。

4、根据全加器真值表,可写出和s,高位进位co的逻辑函数a1a0作为两个输入变量,即加数和被加数ab,d0~d3为第三个输入变量,即低位进位ci,1y为全加器的和s,2y全加器的高位进位co,则可令数据选择器的输入为a1=a,a0=b,1do=1d3=ci,1d1=1d2=ci反,2d0=0,2d3=1,2d1=2d2=ci;一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci1,输出本位和为SiY为全加器的和S,2Y为全加器的高位进位C1,于是就可以令数据选择器的输入为A1=A,A0=B,1DO=1D3=C0,1D1=1D2=C0反,2D0=0,2D3=1,2D1=2D2=C0,1Q=S1,2Q=C1根据对应的。

5、74ls283引脚图及功能真值表如下74ls74功能表,74LS74是双D触发器功能表是用手机填的,前面两个是1,中间4个是0,后面两个是1真值表是逻辑事件输入和输出之间全部可能状态的表格复杂的组合逻辑也有叫功能表真值表是在逻辑中使用的一类数学表,用来确定一个表达式是否为真或有效数字电路;20110529 使用74LS83构成4位二进制全加\全减器 2 20110715 求助使用74LS283构成4位二进制全加\全减器后,怎样 20120607 使用74LS83构成4位二进制全加\全减器 具体要求1 2 20121123 用译码器74LS138实现构成一位二进制可控全加全减器,K= 11 20160523 74。

6、74LS42的功能是十进制译码器74LS283的功能是四位二进制超前进位全加器可以使用单个74ls148芯片的简化真值表和32行5行优先编码器的简化真值表,找出每个块74ls148和74ls148的每个325行优先编码器输出和每个块的 yex 之间的关系使用74lsl148的选通输入 s,选通输出 ys 和扩展 yex,四个。

相关标签 :

上一篇: 完美桌面,完美桌面手机版

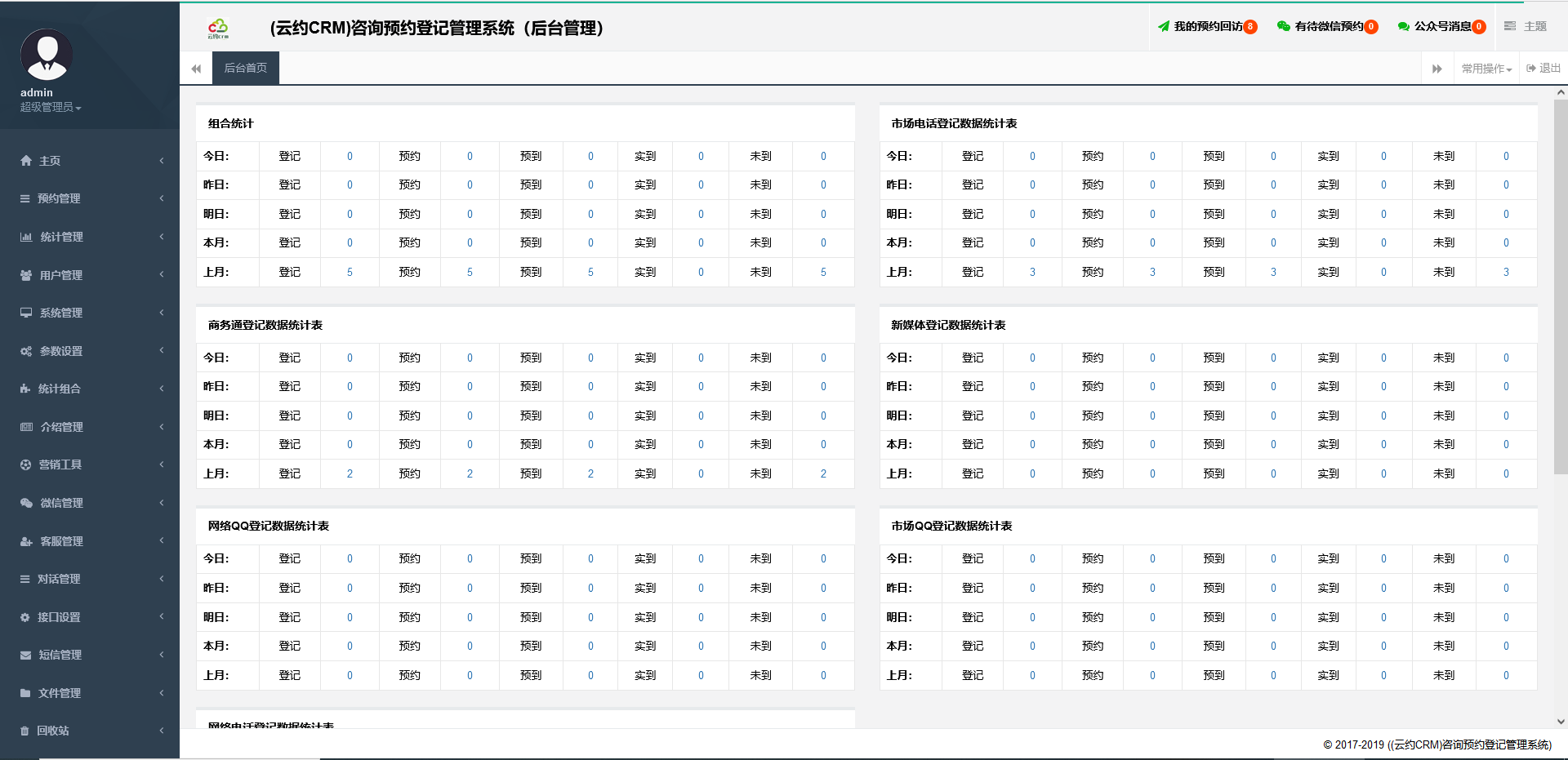

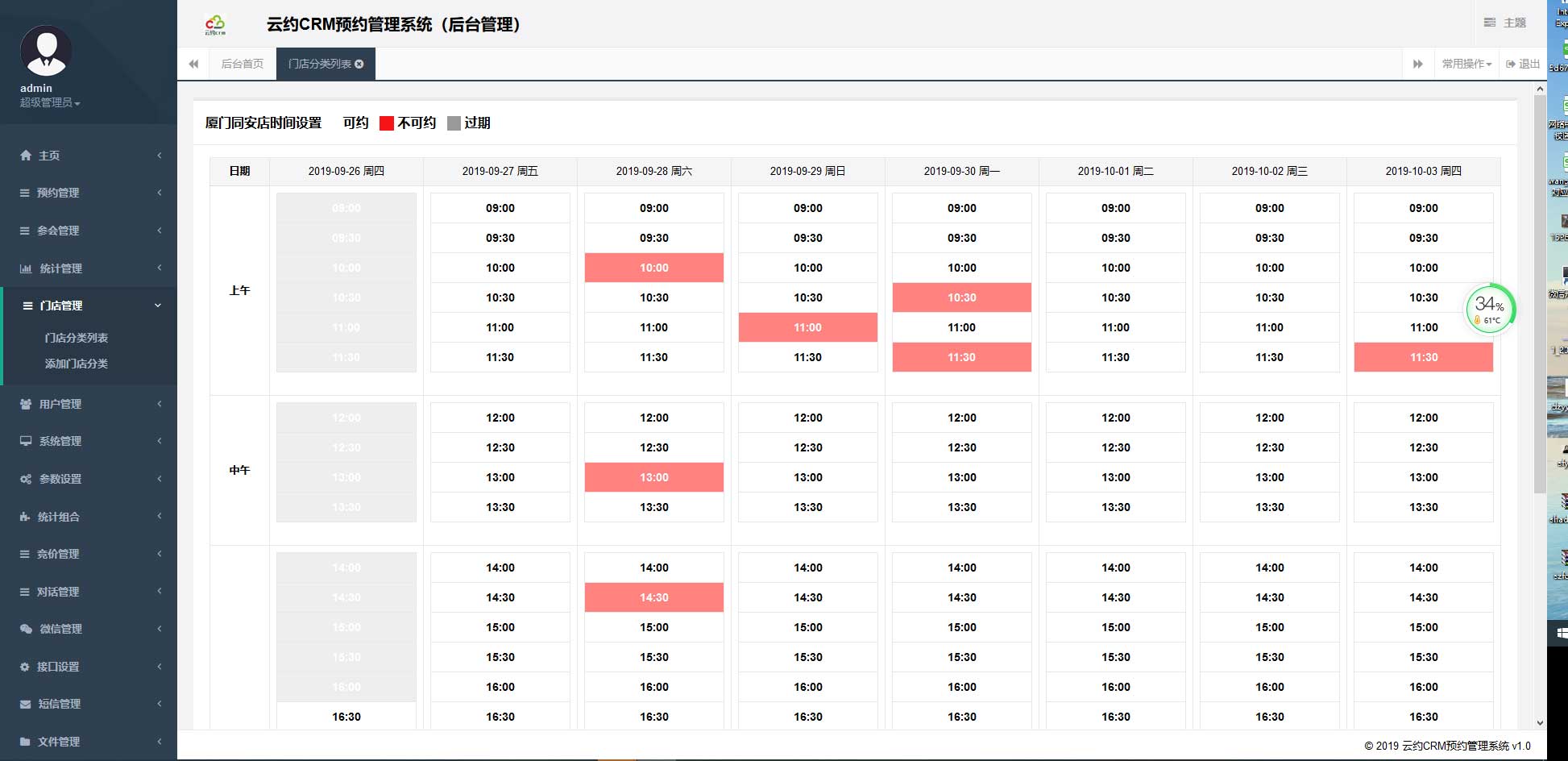

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

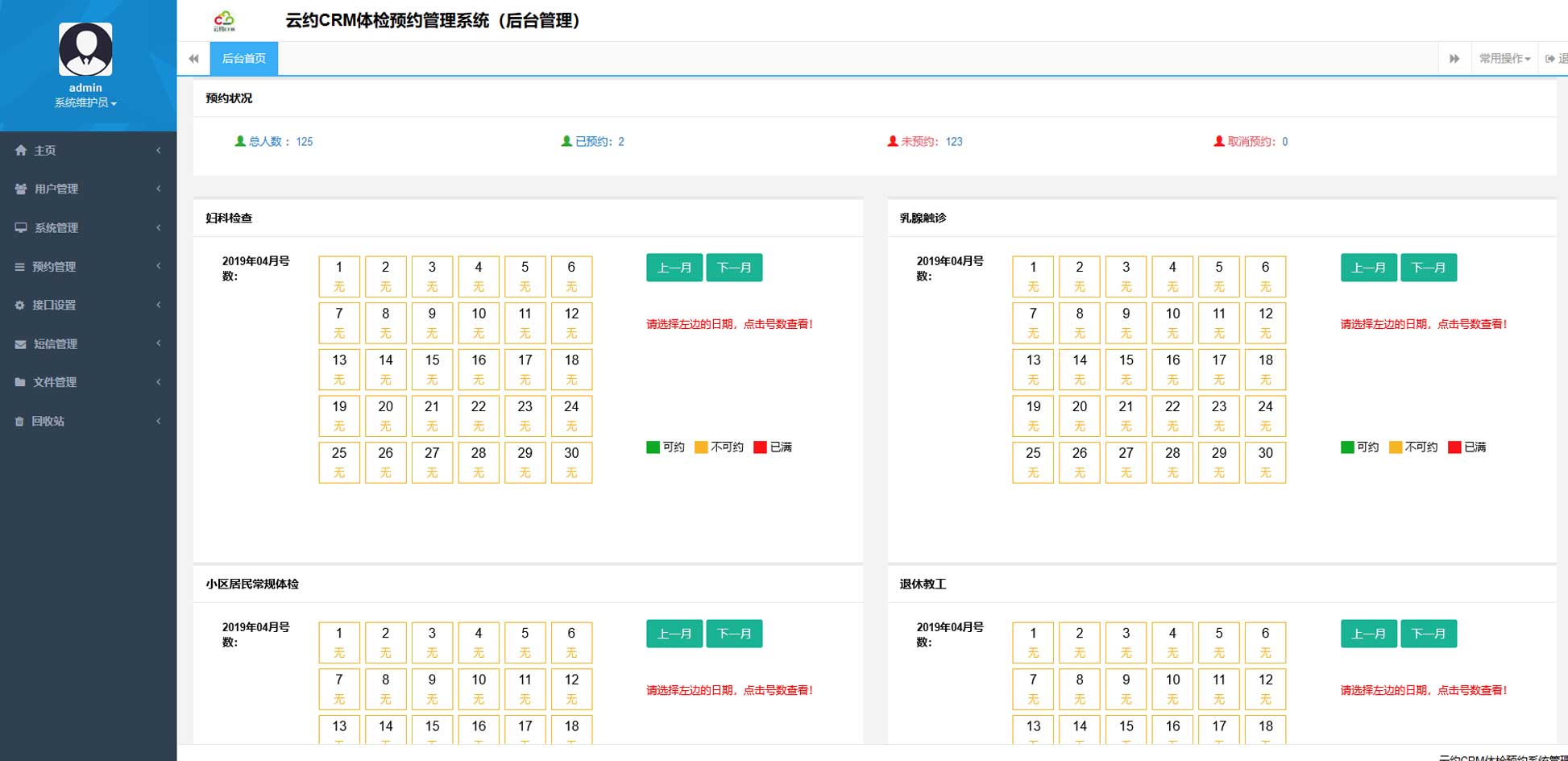

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

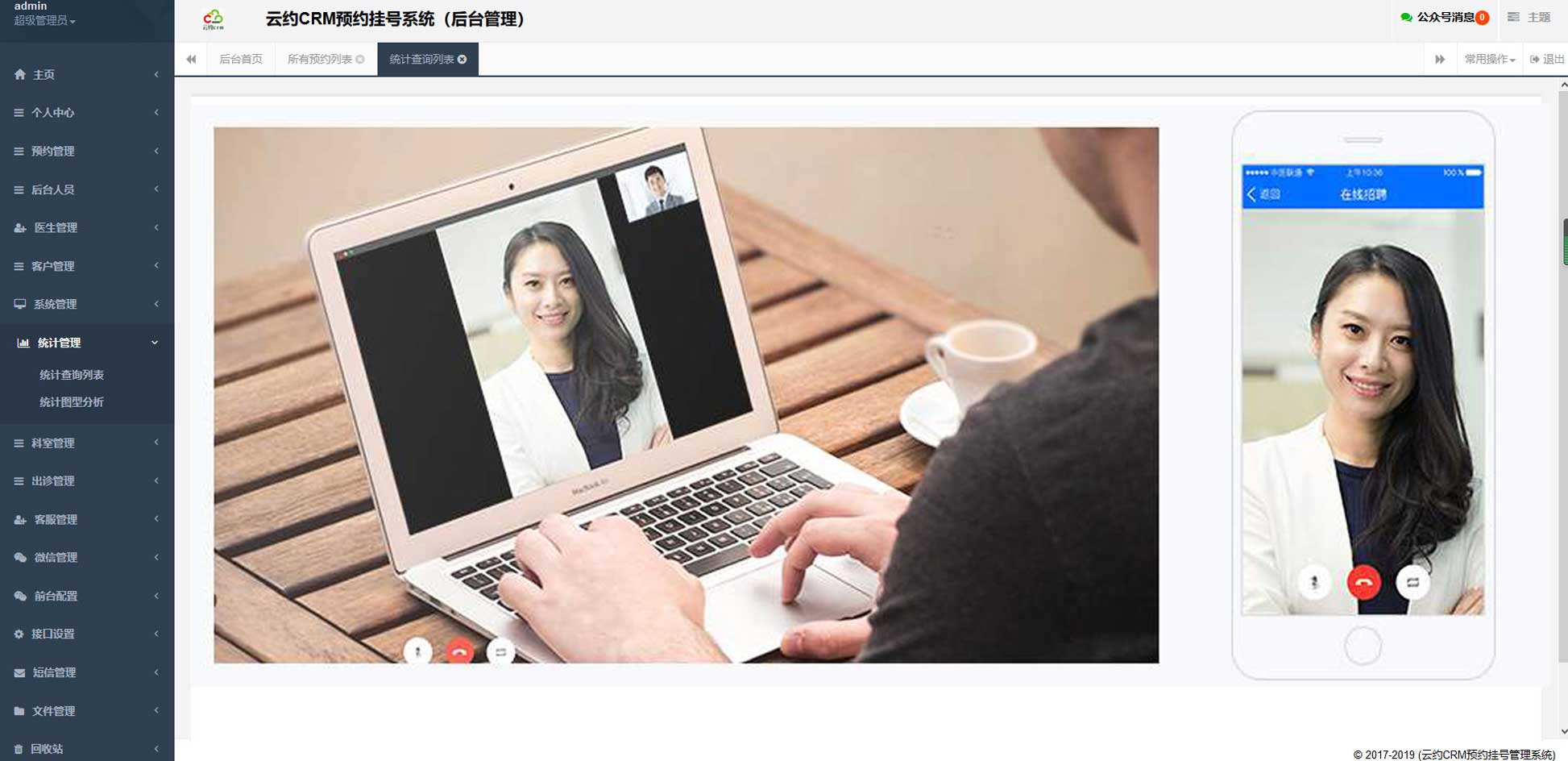

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com