和工作时钟dds信号源,相位累加器位数及输出频率有关 Fout = M*Fc2^NFc为系统工作时钟dds信号源,N为相位累加器位数,M为频率控制字;DDS属于数字化技术,输出波形等,适用于波形发生器,函数发生器,RF信号源,以及基本dds信号源的模拟输出模块DTS也是数字音频技术,适用于音视频的声音视频整合技术输出播放,多声道环绕技术。

信号源分为模拟信号源和数字信号源,模拟信号源采用振荡器来实现,与DA无关,只与LC的范围有关数字信号源采用DDS来实现,最低频率与DA也无关,与内部波形存储器的大小有关,高频则与DA的最大输出频率有关;相位连续性在频率切换时,相位保持连续,避免了相位跳变带来的问题宽带正交信号输出可以输出宽带正交信号,适用于需要同时处理IQ信号的应用场景低相位噪声输出相位噪声低,对参考频率源的相位噪声有改善作用,提高了信号的纯度任意波形产生通过改变波形ROM中的数据,可以产生任意波形,增加了DD。

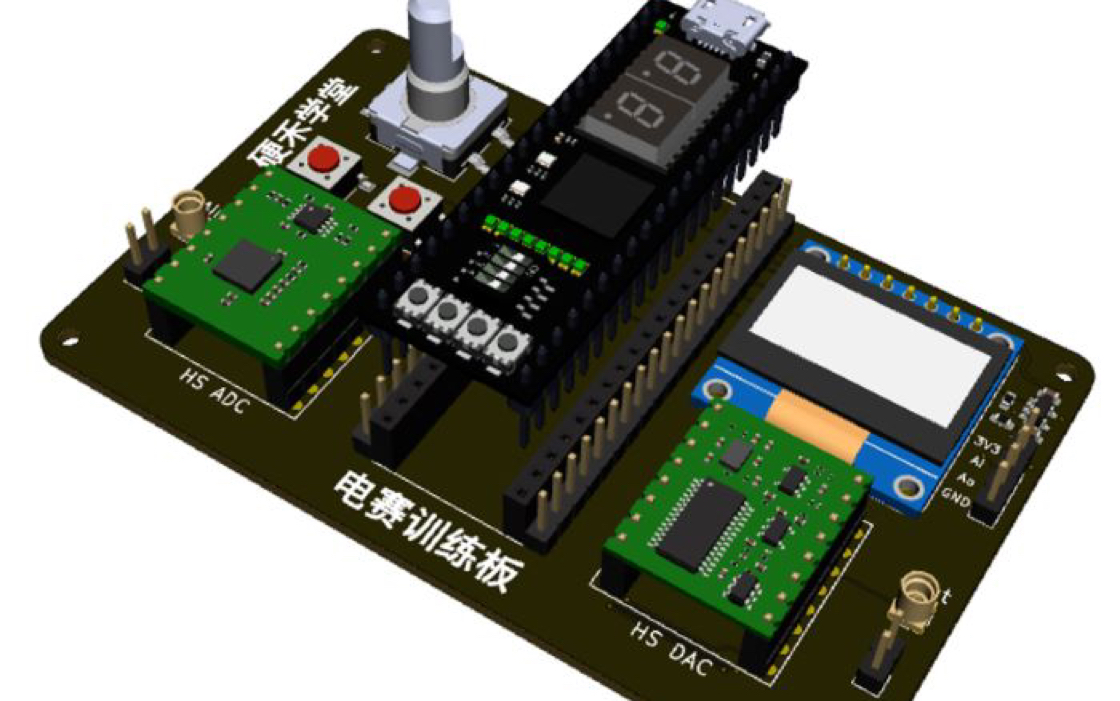

由于DDS是数字化高密度集成电路产品,芯片体积小功耗低,因此可以用DDS构成高性能频率合成信号源而取代传统频率信号源产品近年来DDS技术得到了飞速的发展,各种通用的DDS 芯片不断上市,性能很好,使用简单,价格也在不断下降,给一般用户使用提供了极大的方便,这里给大家介绍一款采用Analog公司的AD9835;1dds指的是数字频率合成技术,它的本质是DDS信号发生器,即是把信号发生器的频率稳定度准确度提高到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的频率调节2另外,采用dds这种方法设计的信号源可工作于调制状态,可对输出电平进行调节,也可输出各种波形更多关于dds指的是什么。

给你几个最吧最容易RC振荡器,电容电阻组成,低频玩玩可以,频率一高直接趴窝最常用石英晶体振荡器性能很不错,虽然精度不如DDS,不过够用而且价格足够便宜,唉呀呀,老板们的最爱啊最容易实现精密控制DDS,这个就是个大号读表器,只要把数据送得够准确,出来信号的质量可是杠杠的最。

1、DDS功放源自德国,DDS品牌创立于20世纪60年代,专注于高端音频领域直接数字合成技术DDS是DDS品牌的核心技术之一,用于生成周期性波形这项技术能够从低频到上百兆赫兹的正弦波和三角波的产生,几乎所有的应用都依赖于DDS芯片,包括购买来的信号源DDS的技术优势在于其精确的频率控制和快速的响应能力它。

2、而数字函式发生器采用直接数字综合 DDS,DAC,数位讯号处理,以及一个单周期存储缓冲器来产生信号 DDS技术依赖数字控制的方法,利用单基准时钟频率来实现一个模拟频率源DDS能够实现高精度和高解析度,高温度稳定度,高宽频,以及随机的和相位连续的频率切换 许多信号源通过对一个内部时基进行整数分频来产生时钟信号。

3、1DDS代表数字直接合成技术,它是一种先进的信号发生器技术DDS信号发生器能够将频率的稳定度和准确度提升至与基准频率相匹配,同时能够在宽广的频率范围内进行精确的频率调整2采用DDS技术的信号源具有多个优点,例如能够进行调制操作,可以调整输出电平,并且能够输出多种波形想要了解更多关于DDS指的。

4、直接数字合成技术DDS是一种频率合成技术,专用于生成周期性波形当前,无论是从低频到上百MHz的正弦波三角波的产生,绝大多数都借助DDS芯片来实现,即使是购买来的信号源,其原理也是基于DDS为了便于理解,以36MHz的时钟MCLK为例,每个脉冲的周期为2778ns接下来,我们附上一个“相位幅度。

1、低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号DDS在相对带宽频率转换时间高分辨力相位连续性正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能如何用FPGA实现 相位累加寄存器是DDS的核心,在我的设计中相位。

2、这种方法在早期的射频信号源中较为常见,但其频率分辨率和灵活性相对较低 直接数字合成DDSDDS仪器使用一个参考振荡器来记录数字电路,其中包括一个数字模拟转换器DAC来直接产生所需的输出频率DDS具有极高的频率分辨率和灵活性,可以快速地切换频率和相位,是现代射频信号源中常用的合成方法 间接合成间接合成利用VCO。

3、1DDS信号发生器输出接被测电路,被测电路的输出经过检波或者直接接到示波器的垂直端,预先设置好信号源为扫频状态设置好中心频率扫描宽度扫频时间一个扫频周期令扫频为线性扫描,示波器主要是调节合适的触发参数2如果信号源的扫频周期刚好等于示波器的扫描时间,触发同步刚好在扫描起点,屏幕。

4、fclk这是输入脉冲频率,也称为定时期中断频率它是DDS系统的工作时钟,决定了系统能够处理信号的最高频率在实际应用中,fclk通常由一个稳定的时钟源提供2^N这里的N代表定时器里面的累加器的位数累加器是DDS系统的核心部件之一,它负责根据频率控制字K进行累加操作N的大小决定了DDS系统的。

上一篇: hadoop,hadoop安装

下一篇: 函数不行,函数不好怎么办

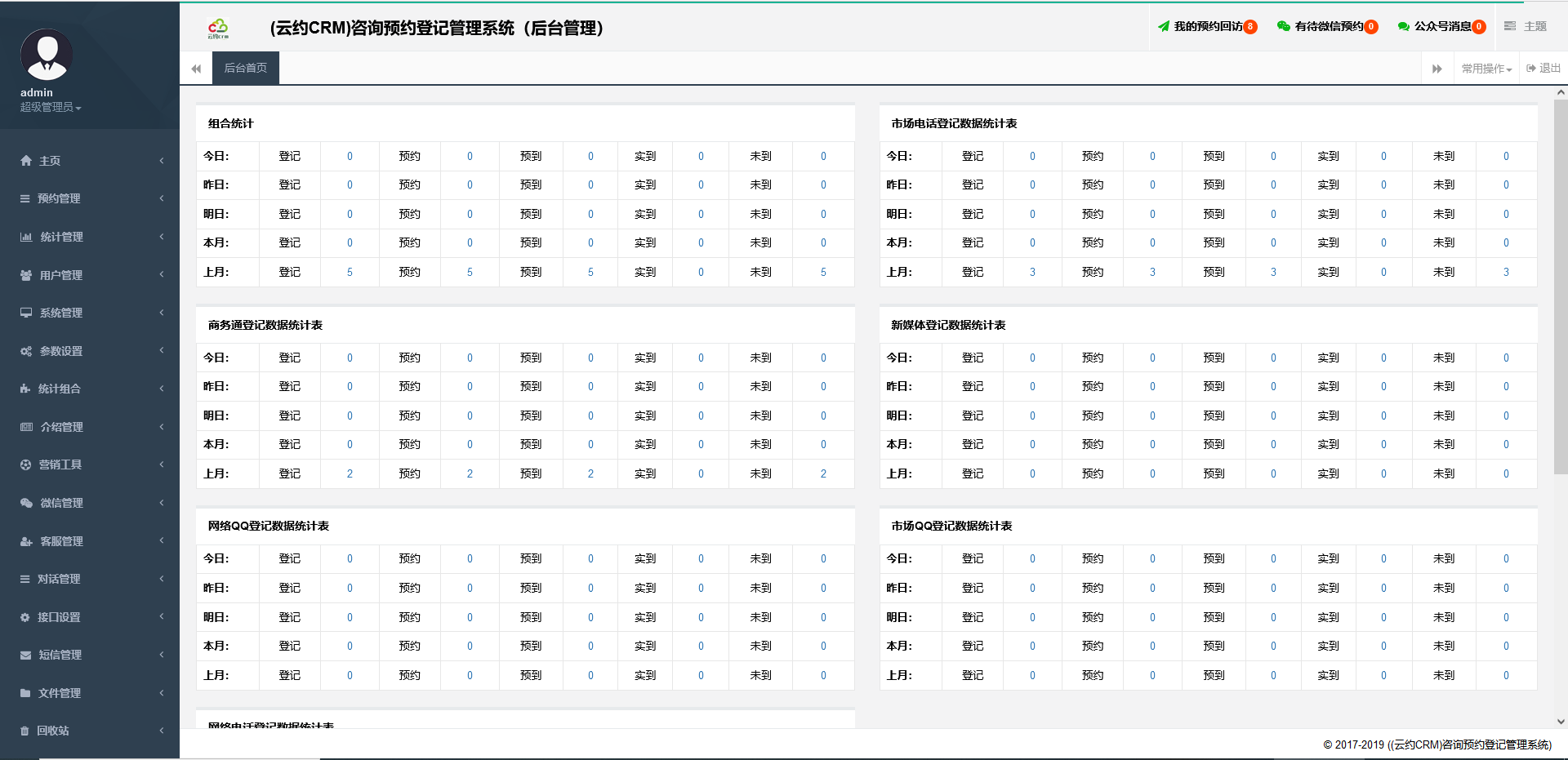

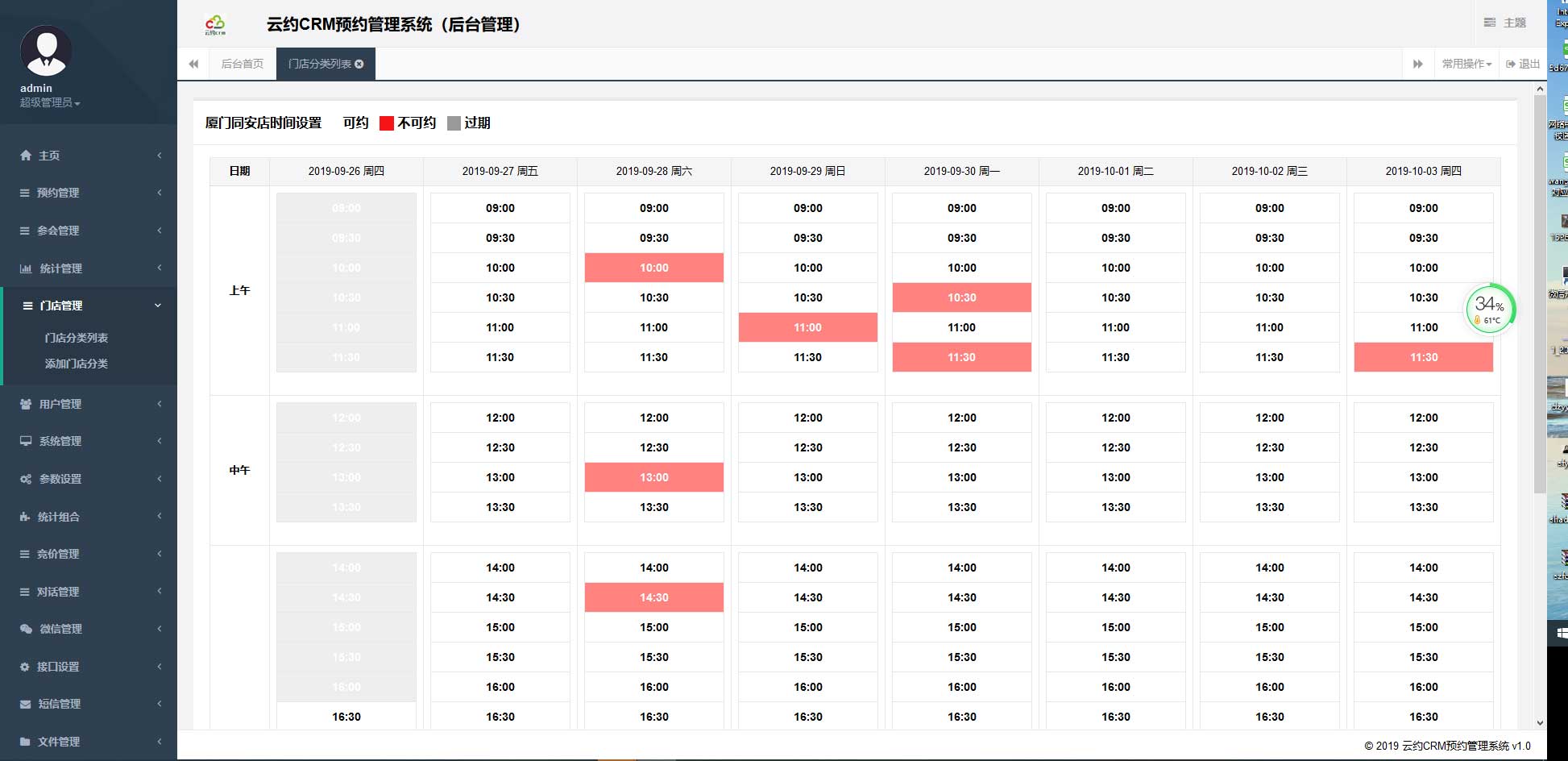

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

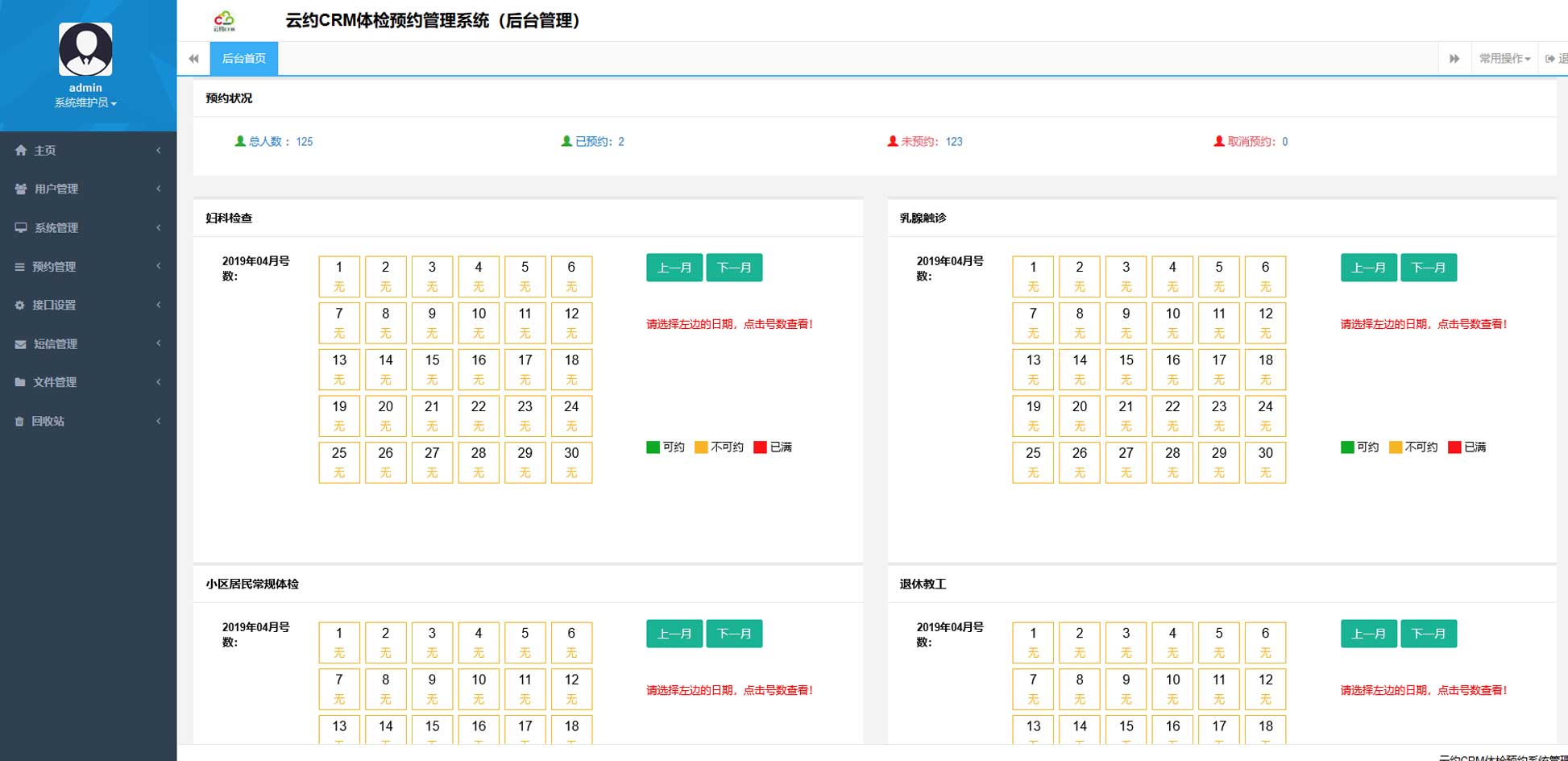

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

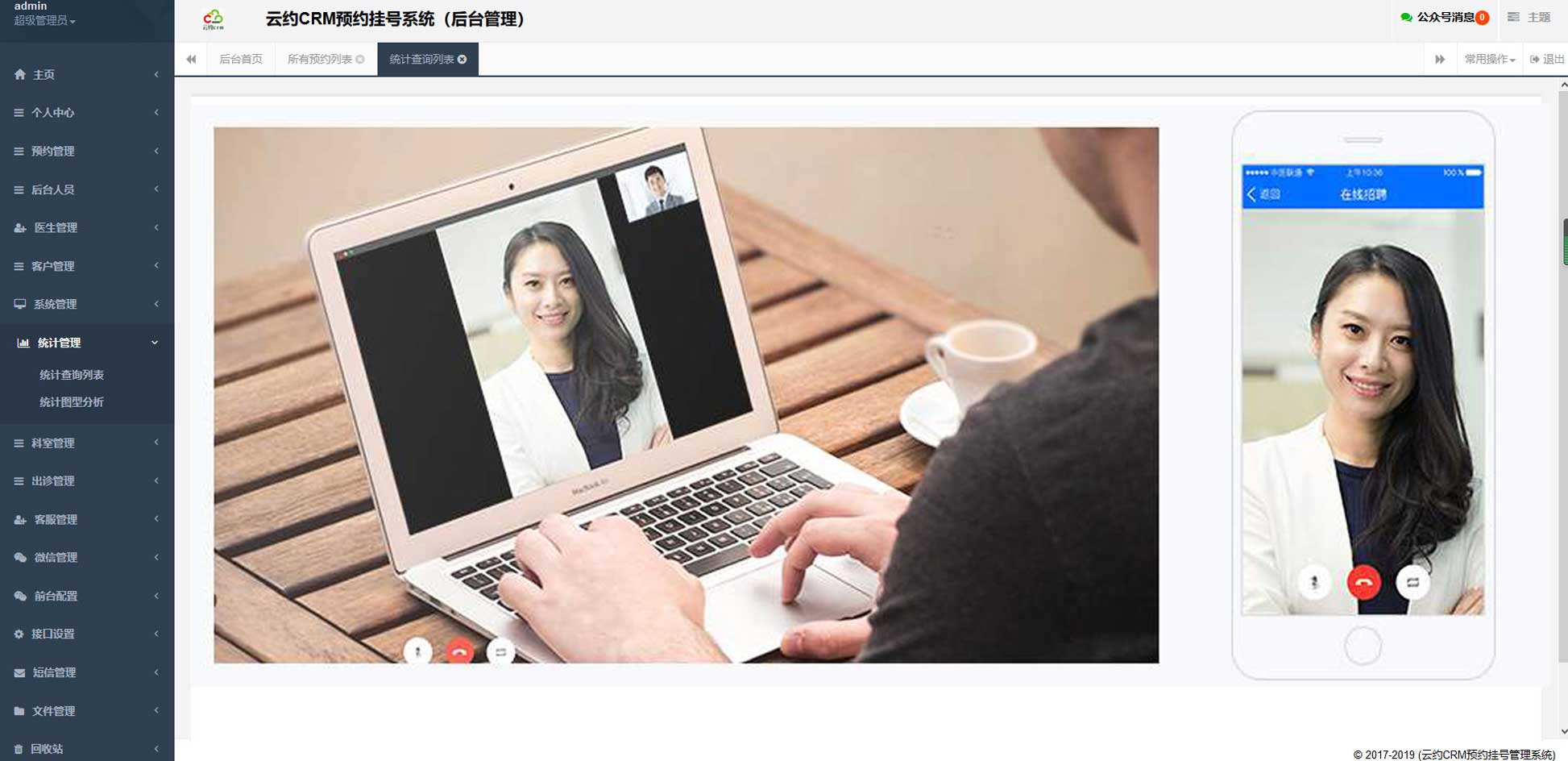

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com