目前为你的FPGA设计加加速,NIC、Router、Switch任意实现-,在众多电子产品中,采用FPGA+FX3搭配方式来实现USB30接口相当流行赛普拉斯官方数据手册对FX3的描述如下EZUSB FX3配备了一个可完全配置的并行通用可编程接口GPIF II,该接口可与处理器ASIC或FPGA连接GPIF II是赛普拉斯USB 20产品FX2LP中的GPIF的增强版本,可轻松连接到多种常用接口,例如为你的FPGA设计加加速,NIC、Router、Switch任意实现-;GigE Vision的优势 得益于IEEE标准化与GigE解决方案的成功,制造商在硬件软件与附件方面拥有众多选择例如,GigE Vision解决方案可直接连接100GigE相机,利用现成的NIC或FPGA卡降低系统复杂性在对更先进机器视觉的需求推动下,图形处理单元GPU在涉及高速度3D成像与深度学习的应用中得到了广泛应用。

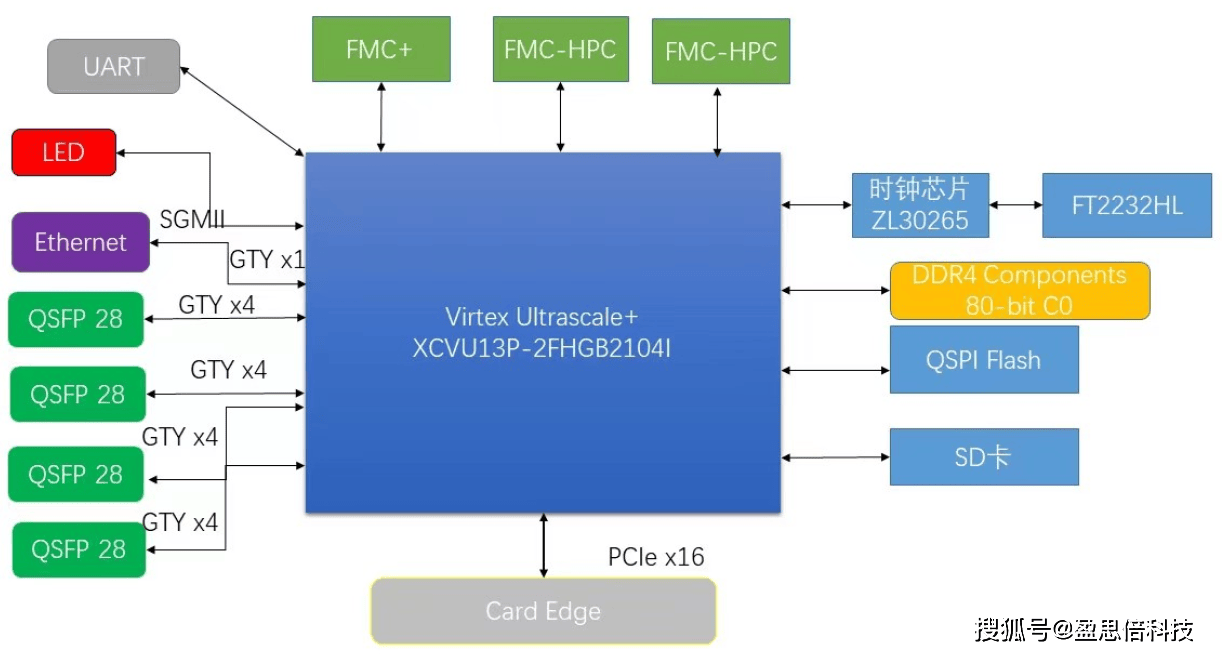

IP定义为用于ASIC或者FPGACPLD中预先设计好的电路功能模块IP分为软IP固IP硬IP 软IP核用Verilog HDL描述的功能模块 固IP核完成了综合功能模块,有较大的涉及深度,以网表文件的形式提交给客户使用 硬IP核提供设计最终端产品掩膜编辑本段IP寄存器 IPInterrupt Priority 中断优先级控制;软硬件融合对SmartNICDPUIPU的定义基于设计规模与功能的逐步增强,从基础网络设备发展至更高级别处理单元SmartNIC提供卸载网络任务的能力,DPU进一步扩展至卸载IO底层处理,而IPU更专注于业务加速,eIPU则实现任务引擎间的高度均衡与灵活交互在软硬件融合框架下,DPUIPU成功的关键在于平衡性能与灵活性;本设计采用纯verilog实现的25GUDP高速协议栈,专注于提供25GUDP回环通信测试它旨在为用户提供一个高度可移植功能丰富的25GUDP协议栈架构,支持用户根据需求创建自己的项目该协议栈基于主流FPGA器件,提供了一系列工程源码,适用于Xilinx系列FPGA,使用Vivado作为开发工具核心资源为GTY,同时支持SFP。

Protel DXP 2004已不是单纯的PCB印制电路板设计工具,而是由多个模块组成的系统工具,分别是SCH原理图设计SCH原理图仿真PCB印制电路板设计Auto Router自动布线器和FPGA设计等,覆盖了以PCB为核心的整个物理设计该软件将项目管理方式原理图和PCB图的双向同步技术多通道;Cadence Allegro是Cadence推出的高级PCB设计工具,结合了Cadence Capture等前端产品,为复杂PCB设计布线提供了完美解决方案它几乎涵盖了电子设计的所有方面,包括ASIC设计FPGA设计和PCB板设计,展现了在仿真电路图设计自动布局布线版图设计及验证方面的优势Eagle是一款历史悠久始于1988年的EDA设计;一方面,通信技术,标准,芯片更新的太快了,快到为你的FPGA设计加加速,NIC、Router、Switch任意实现-你根本来不及系统的了解它,只能通过特定的项目,需求进行了解另一方面对于公司来说,需要做的硬件产品也是变化很快,客户需要T1, E1, PDH, SDH,Ethernet, VoIP, Switch, Router, 没有人是什么都懂的,都需要能够结合客户的需求,选择的芯片方案进行详细了解,尤其对于接口。

Achronix公司表示,pipoPIPE可加速数字在FPGA结构中通过的速度,通过使用一种简单的握手协议来控制数据流,整个过程无需全局时钟尽管该器件的内部工作有着根本性的不同,但设计时完全可使用硬件描述语言,如RTL等Semico Research公司的高级分析师Rich Wawrzyniak表示,“他们在做一些FGPA业内很独特的事情。

上一篇: ts3,ts3380墨水灯闪烁怎么消除

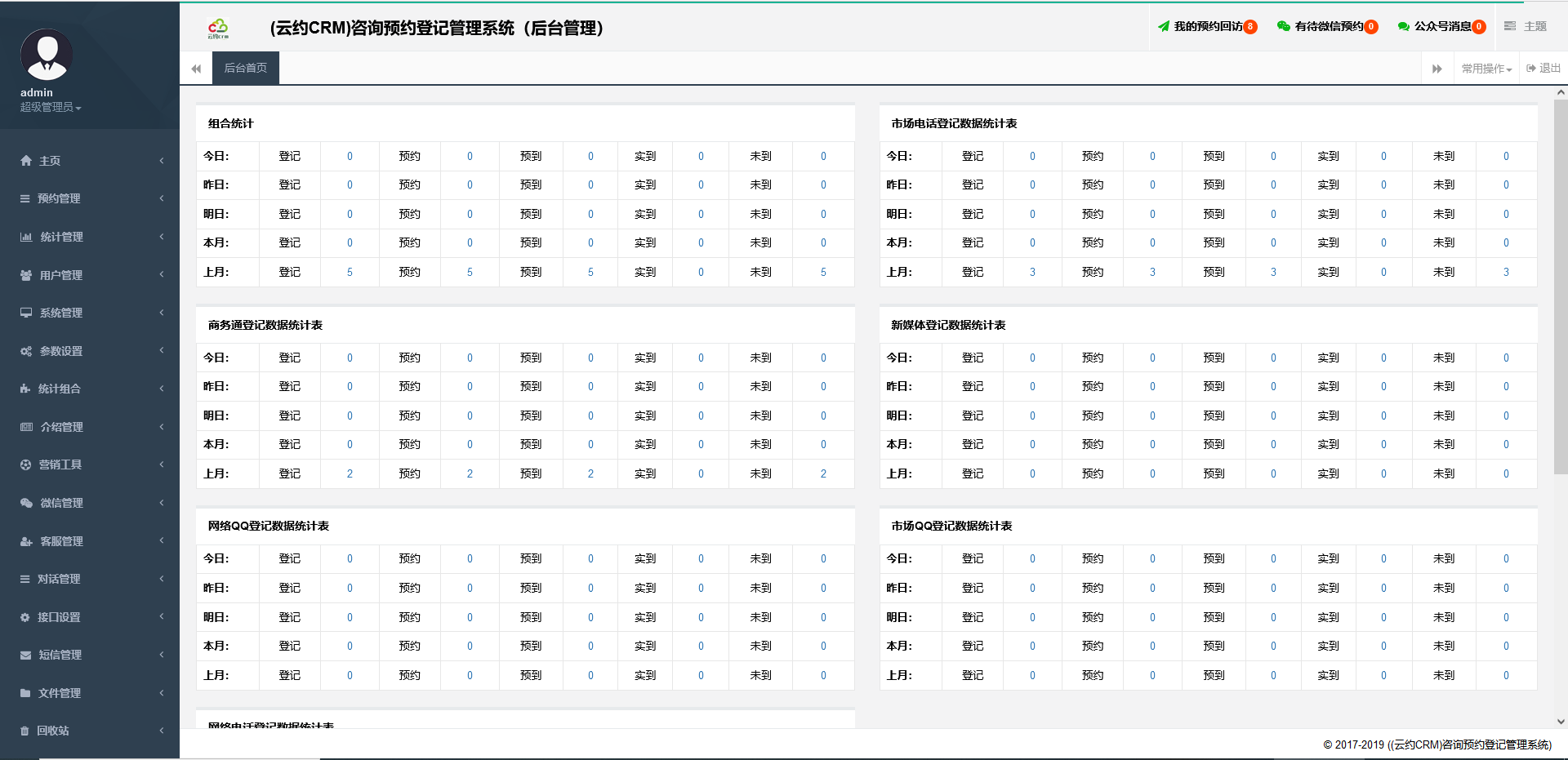

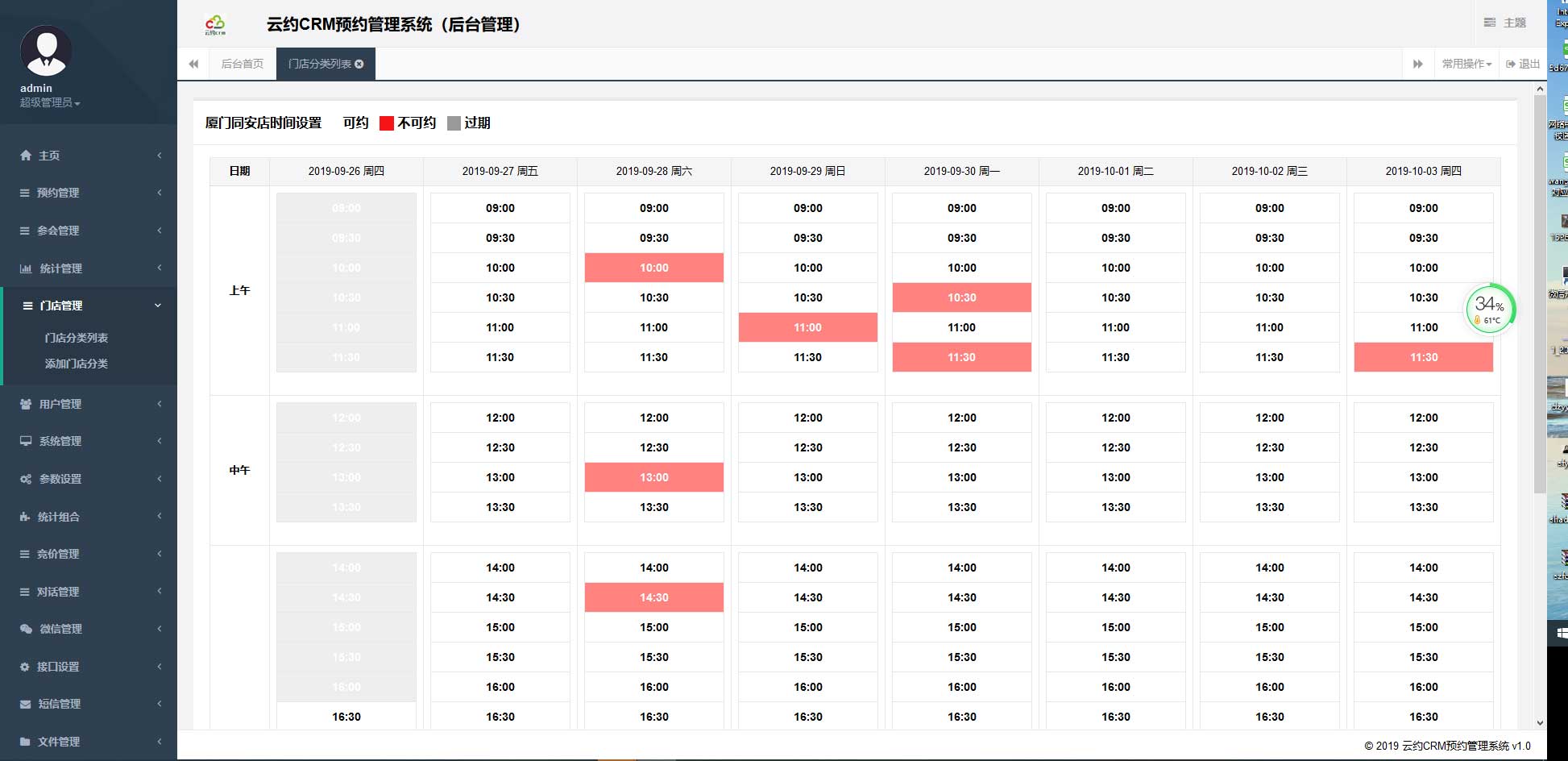

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

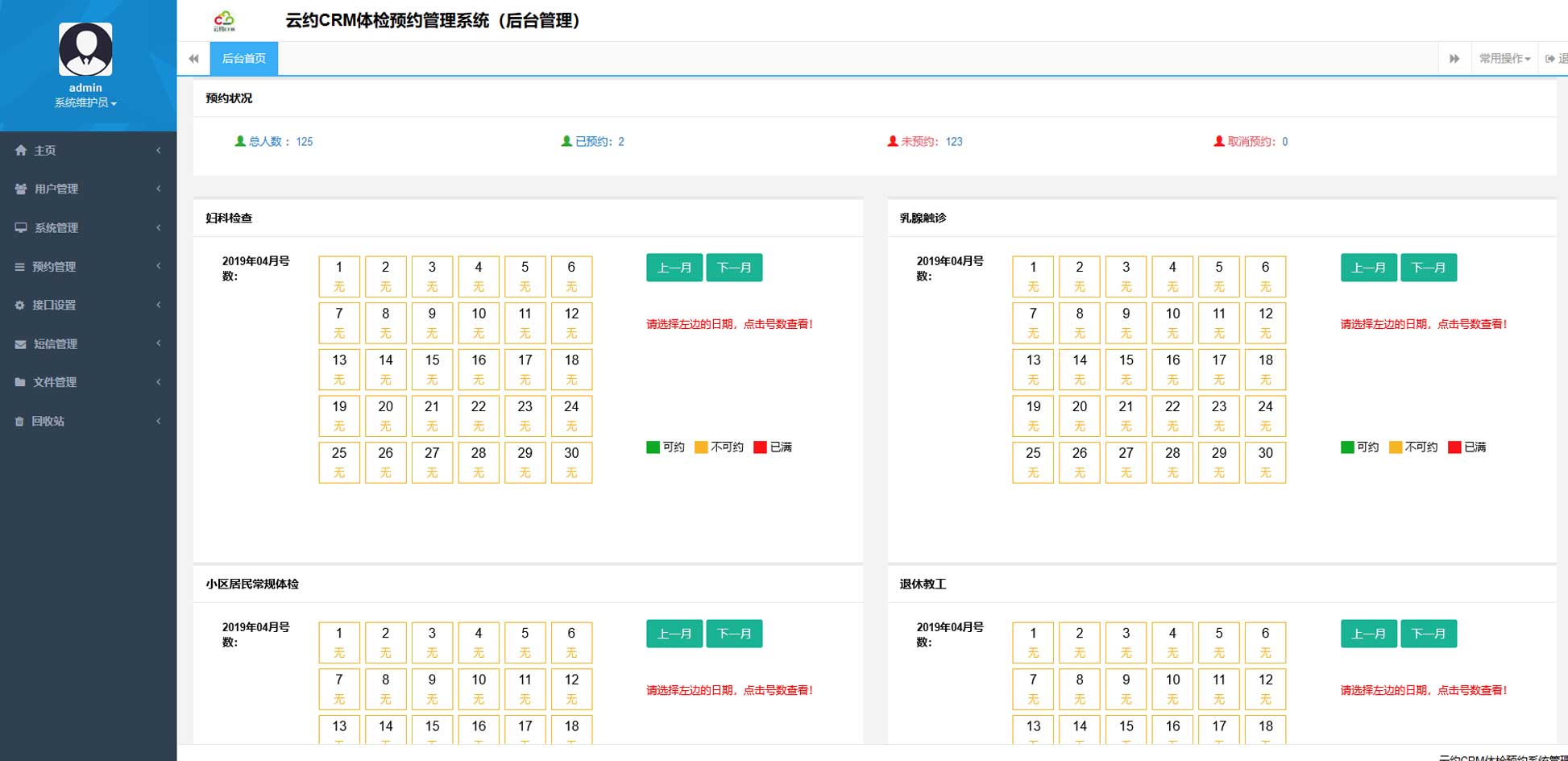

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

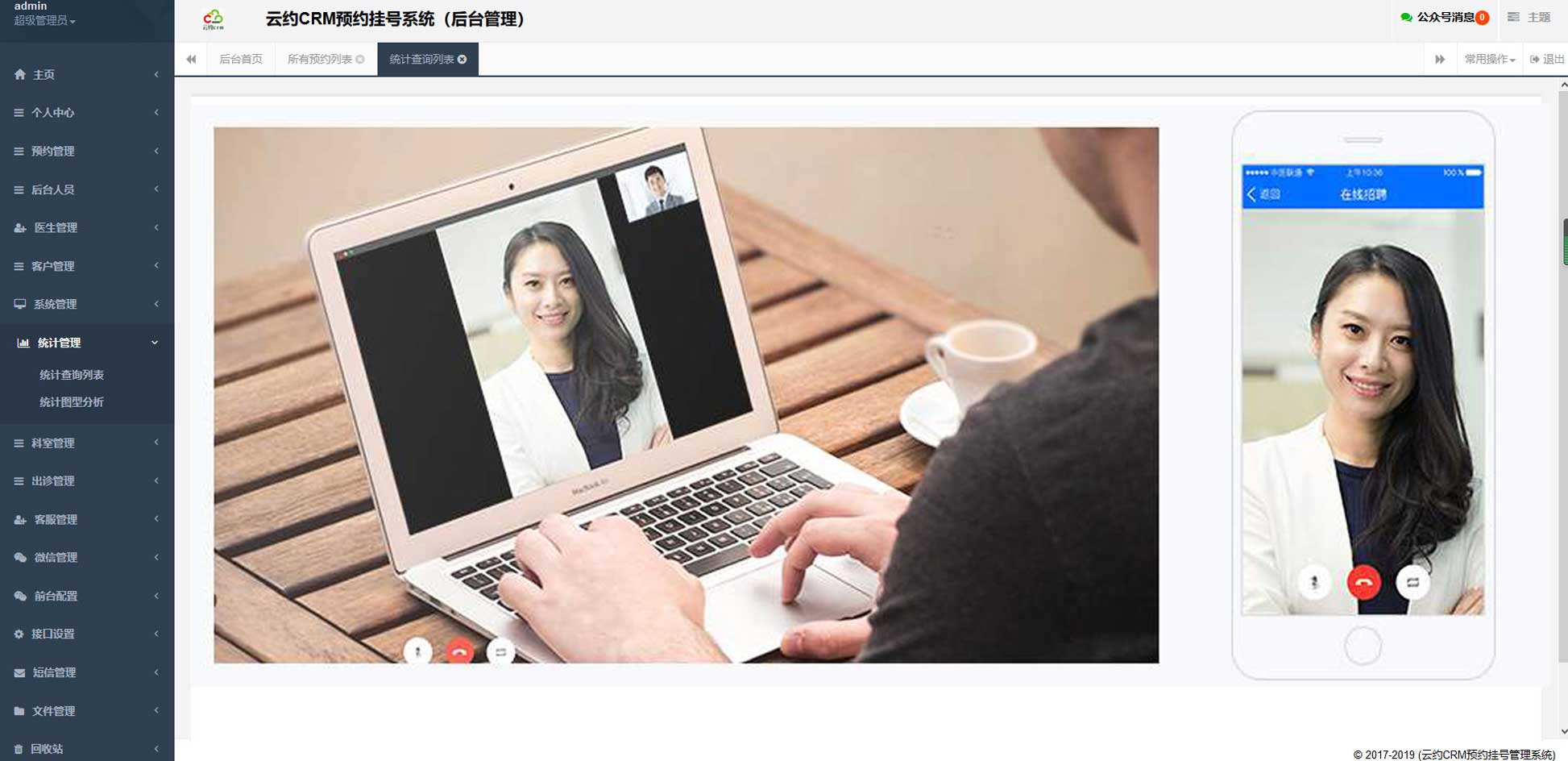

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com