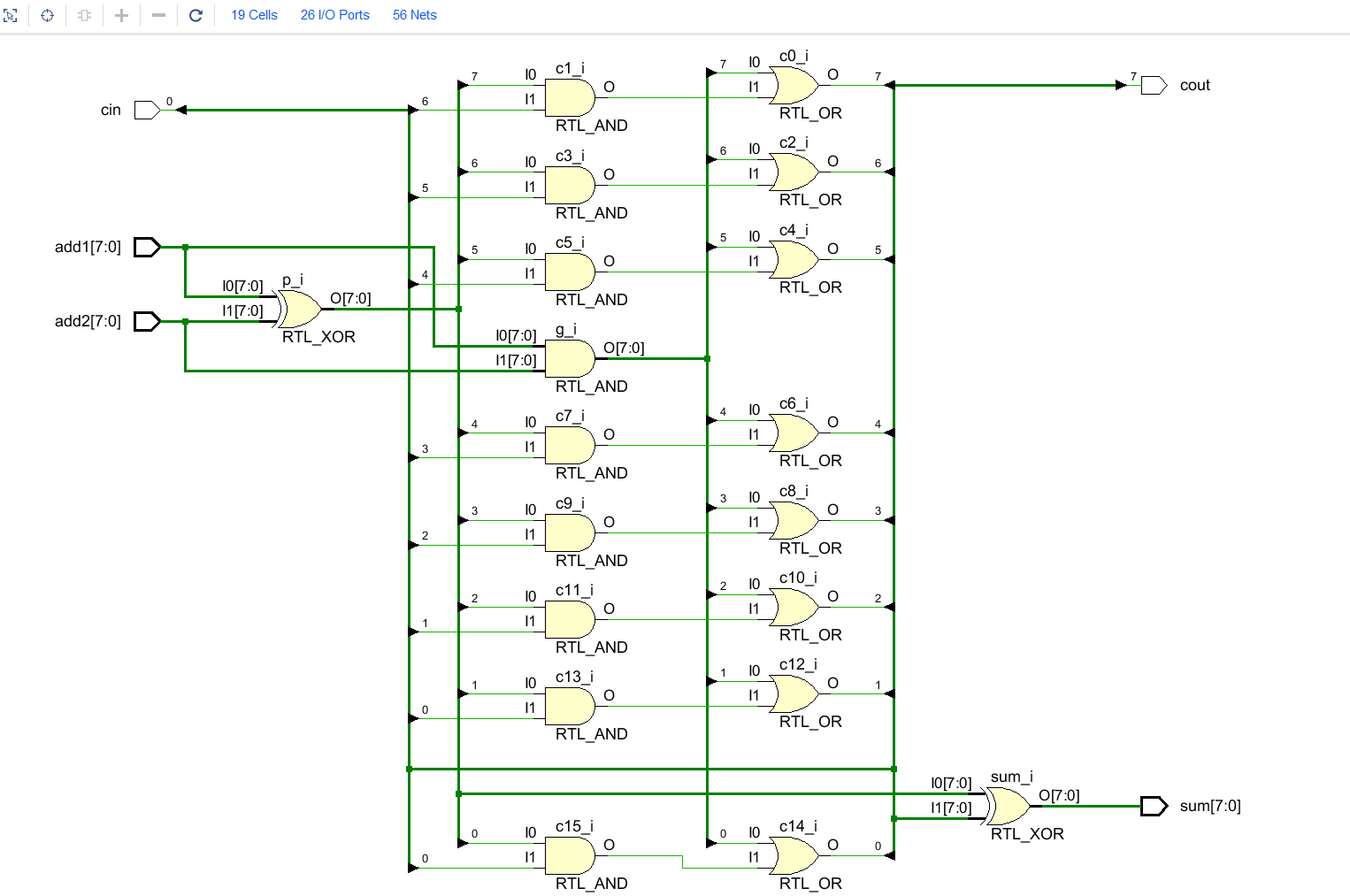

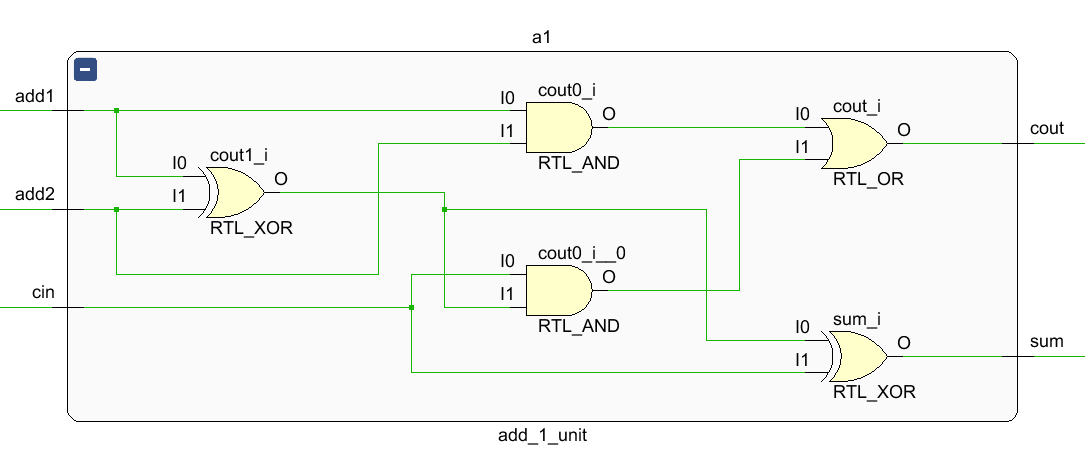

为行波进位加法器了提高计算速度行波进位加法器,现代计算机采用超前进位加法器替代行波进位加法器行波进位加法器,以减少每次进位所需的时间超前进位加法器的设计使得计算机能够实现更快的加法运算,从而支持每秒几十亿次运算的高效率计算ALU的抽象设计简化了工程师的工作,不再需要关注底层逻辑门的组成,使得设计过程更加高效ALU的图示通常采用抽象;行波进位加法器是一种用于实现加法的装置,它能够产生数的和在进行加法运算时,加数和被加数作为输入,而和数与进位则作为输出对于1位的二进制加法,涉及到五个量被加数A被加数B前一位的进位CIN此位二数相加的和S以及此位二数相加产生的进位COUT其中,前三者是输入量,后两者是输出量。

该进位加法器的工作原理如下当M等于0时,行波进位加法器执行正常的加法运算,即A和B的和以及对应的进位Cout2当M等于1时,行波进位加法器执行减法运算此时,A和B之间的差值A与B需要转换为加法运算;超前进位加法器为了提高计算速度,现代计算机采用超前进位加法器替代行波进位加法器,以减少每次进位所需的时间,从而实现更快的加法运算抽象设计ALU的抽象设计简化了工程师的工作,使得设计过程更加高效图示通常采用抽象符号表示,如“大V”形状,展示其内部结构和功能历史发展著名的ALU之一是英特尔。

这种特性使得光学处理器的各个区域能独立执行逻辑运算,实现数据并行处理,这在电子计算机中难以实现而且,光学处理器可以无缝拼接,形成更大规模的处理器,避免了电子计算机中“核间通信”和“同步”问题尽管有众多数据位的优势,但三值光学计算机在算术运算上面临挑战,特别是行波加法器的进位延迟问题;进制的减法运算的原理1在计算机内部做减法时是用加法做的123就是+123n个1位的全加器FA可级联成一个n位的行波进位加减器M为方式控制输入线,当M=0时,作加法A+B运算当M=1时,作减法A-B运算,在后一种情况下,A-B运算转化成A补+-B补运算,求补。

在HDLBits刷题过程12635中,重点内容及解答如下模块层次与进位加法器CSA与行波进位加法器比较CSA相比行波进位加法器具有更小的延迟,但会占用更多的逻辑资源加减法器构建理解加减法器的构建方法,特别是如何利用异或门实现按位取反和减法操作过程块与逻辑描述组合always块用于描述组合逻辑;在日常用语中,“行”字有多个读音,包括xíng和háng但在专业术语和特定上下文中,读音通常是固定的在行波进位加法器这个术语中,“行”读作xíng,以符合其描述信号流动的含义为了更清晰地理解,可以想象一个波形在水平线上前进,这里的“行”就是波形前进的路径,与“行波进位加法器”中的“行”有着相似的意象因此,读作xíng更为贴切。

您是想问n位行波进位加法器的特点是什么吗这个加法器特点如下行波进位加法器是把n位全加器串联起来,低位全加器的进位输出连到相邻的高位全加器的进位输入各位相加是并行的,但其进位信号是由低位向高位逐级上升;减法操作开始,最低位的全加器首先执行操作最低位的全加器的一个输入端需要等待取反异或门的输出,时延为 3T接着,被减数到达全加器的输入端,从加法器输入端到进位输出的总时延为 8T3T 取反 + 5T 全加器进位,完成进位后,最低位的计算值输出需等待 9T3T 取反 + 6T 计算值输出。

阵列乘法器的核心是通过逐位相乘并将结果逐列累加,使用与门生成部分和,然后通过半加器或全加器进行加法运算4比特AB乘法的示例展示了这个过程,其中aibi表示两个比特的与运算结果RCA阵列乘法器中,进位通过行波进位加法器传播,消耗资源包括与门半加器和加法器而CSA结构通过优化进位计算,减少了。

与门用于生成部分积,即两个数的每一位进行与运算半加器和全加器用于对部分积进行加法运算,得到最终的乘积结构类型RCA结构在这种结构中,进位是通过行波进位加法器传播的它消耗的资源包括与门半加器和加法器,但可能会因为进位传播而增加延时CSA结构这种结构通过优化进位计算,减少。

在计算机中,并没有减法器所有的减法运算,都是用加法器来完成的用加法器,来实现减法运算,其关键是舍弃进位比如27 + 99 = 一百 26,舍弃进位后就是27-1 = 26舍弃了进位,就是减去了 100,你再加 99,它也就是“-1”舍弃了进位,用正数,就能代替负数,用加法,就能。

而234号全加器的Cin全部来自前一个全加器的Cout,只有等到1号全加器运算完毕,234号全加器才能依次进行进位运算,最终得到结果 这样进位输出,像波浪一样,依次从低位到高位传递, 最终产生结果的加法器,也因此得名为 行波进位加法器 RippleCarry Adder,RCARCA的优点是电路。

行波进位加法器原理是一种高效的二进制加法器设计,它通过并行处理和传播进位来加速加法运算行波进位加法器的基本原理是将加法运算中的进位传播过程并行化,从而提高了加法器的运算速度在传统的逐位进位加法器中,每一位的加法运算都需要等待前一位的进位确定后才能进行,这导致了运算速度的瓶颈而行波。

行波进位加法器Nbit加法器通过组合1bit全加器实现每个全加器的输出进位cout作为下一个全加器的输入进位cin对于16比特加法器,结构如下图所示,其中A和B为加数,S为和,c16为输出行波进位加法器结构简单,只需级联全加器,但存在长进位链的缺点,限制了性能了解更多内容,关注“纸。

行波进位加法器的特点在于其简单的多比特结构,n比特的RCA仅需n个全加器,但随着比特数增加,线性增长的硬件开销和延时成为显著问题以下是1~5比特行波进位加法器的硬件开销和关键路径延时的具体数据,这显示了其性能随着规模扩大的影响值得注意的是,由于加法和减法的等价性,只需在加法器的基础上添加。

上一篇: 窗口颜色,窗口颜色和外观

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

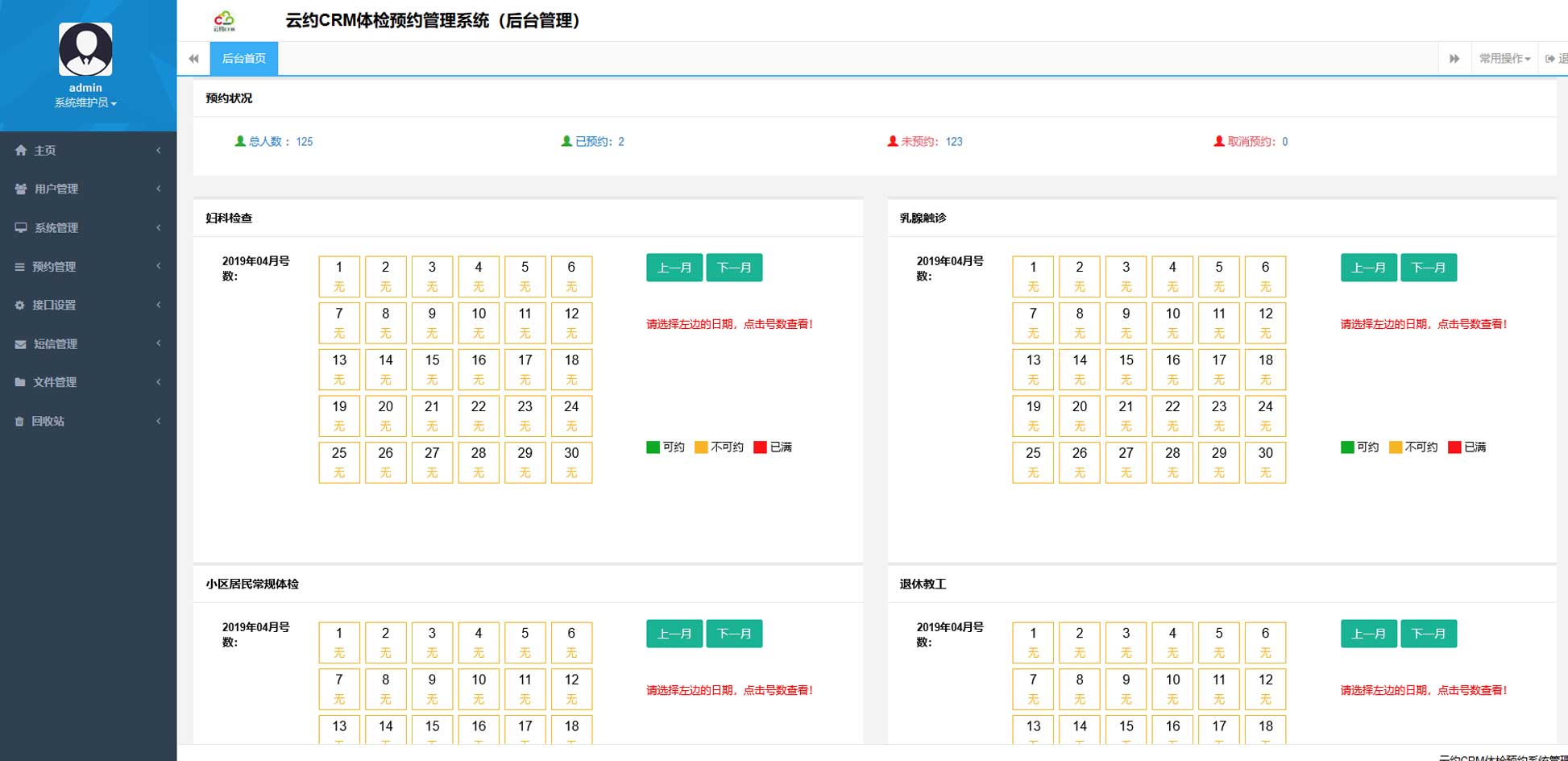

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

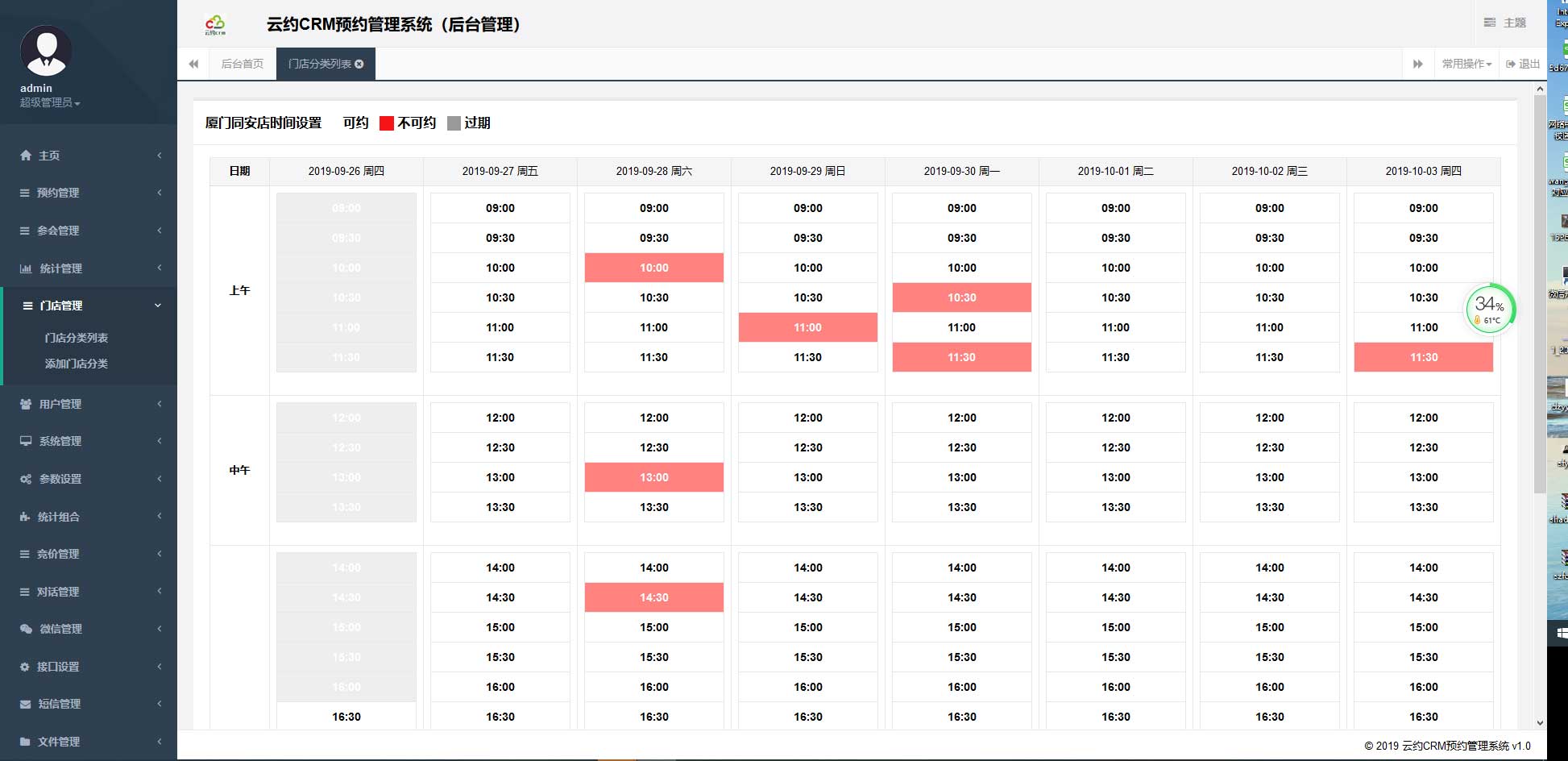

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com