always@posedge clk or posedge clrb表示 清零端是高电平有效,posedge代表上升沿negedge代表下降沿代表clrb异步复位信号,如果没用posedge clrb,为同步复位信号,就是需要时钟跳变时,输出才发生变化触发器复位有高电平有效,也有低电平有效;在Verilog语言中,@和always @都表示对上升沿触发posedge的敏感但是它们在代码块的应用中存在差异前者通常在条件语句或任务中使用,而后者用于描述始终块的行为1 @的用法该语法常常用于事件触发语句中例如,在某个特定的事件发生时执行某个动作或任务这种用法通常出现在过程块内部,作为条件语句的一。

always@敏感事件列表 用于描述时序逻辑敏感事件上升沿 posedge,下降沿 negedge,或电平敏感事件列表中可以包含多个敏感事件,但不可以同时包括电平敏感事件和边沿敏感事件,也不可以同时包括同一个信号的上升沿和下降沿,这两个事件可以合并为一个电平敏感事件在新的verilog2001中“,”和“or”都可以;他们的区别在代码写法上主要是敏感列表的区别,如下示例所示 异步清零always@posedge clk or negedge rst begin ifposedge!rst out lt= 0else begin ···end end 同步清零always@posedge clkbegin if!rst out lt= 0else begin ···。

本文主要探讨Verilog中的边沿检测及其在实际应用中的示例首先,让我们理解Verilog边沿检测,它是一种用于检测输入信号状态变化的重要技术,常用于实现时序控制数据采集和数字信号处理等功能实现Verilog边沿检测的核心在于使用敏感表达式,如posedgenegedge和edge等其工作原理是通过触发器监测信号变化,并;同一个always语句的触发条件,也就是@后面的内容必须统一,要么为沿触发,要么为组合逻辑数值改变触发,这是规定要么写成always @ posedge clk or negedge rst要么写成always @ *因为。

always @a or b or c begin do_somethingend 表示不停地监测abc,一旦它们任何一个发生变化,就立刻do_something,并且这个“监测”是始终存在的这种电路综合出来时组合逻辑电路 always @posedge clk begin do_somethingend 表示不停地监测clk的上升沿,一旦监测到,就立刻do;在Verilog设计中,quotposedgequot是一个重要的时钟边沿触发器,常用于always块的条件语句中当你需要监控信号如THR的上升沿触发执行某些任务时,使用posedge可以帮助你精确控制程序的执行时机例如,你可能会写成always @posedge THR 当THR上升沿到来时,执行这里的代码 你的程序逻辑 always。

1、就是时钟沿上升时触发always后面的语句always后面是敏感值列表posedge是正沿的意思,你拼错了clk应该是时钟的周期信号吧表示时钟的上升沿到来时下面的语句就触发了。

2、posedge一般都用于always@的括号内,表示THR的上升沿到来时,运行always快内的程序如果需要用到THR的上升沿来作为判断条件,建议你仔细点写代码Always包含一条或多条语句过程赋值任务使能ifcase和循环语句这些语句在仿真运行中重复执行由定时控制管理语法alwaysStatement在何处使用moduleltHEREendmodul。

3、数字“1”的那一瞬间时刻叫作上升沿硬件描述语言 在Verilog等硬件描述语言中,用“posedge”表示“上升沿”2数字电路中,数字电平从高电平数字“1”变为低电平数字“0”的那一瞬间叫作下降沿硬件描述语言 在Verilog等硬件描述语言中,用“negedge”表示“下降沿”。

4、你那样写有语法错误很正常啊,posedge一般都用于always @的括号内,表示THR的上升沿到来时,运行always快内的程序,你如果需要用到THR的上升沿来作为判断条件,建议你这样写代码reg THR1reg THR2always @ posedge clk_1M or negedge reset_n if !reset_n begin THR1 lt= 1#39b0TH。

不可以,因为一般你的always块是上升沿触发的,在一个上升沿中捕捉另一个上升沿,是不太现实的你可以给他来个缓存赋值,通过判断此刻的值和上一个时钟时的值是否不同,来实现判定某个变量变化的目的可以。

Posedge用来作为时钟使用的相当于触发器的时钟输入端要检测信号上升沿的话,可以采用以下方法always@posedge clk or negedge rstif!rstbegin sign_1b lt= 1#39b0 sign_2b lt= 1#39b0 end else begin sign_1b lt= sign sign_2b lt= sign_1b end always@posedge clk or negedge。

可以的,同一个敏感信号表中类型一样就行,posedge和negedge都是边沿触发 对于。

在Verilog HDL等硬件描述语言中,最常用的两种事件分为电平触发和边沿触发,其中边沿触发即包括上升沿触发下降沿触发上升沿触发的写法是在符号“@“之后加上”posedge 信号名”,其中“posedge”表示信号的上升沿。

在Verilog中,@posedge语句用于在特定边沿触发事件时执行操作它能够检测四种边沿状态01xz那么@posedge包含哪些情况呢根据Verilog2005标准的972节Event control部分的定义posedge在以下四种情况下会被检测到从1到xz或0,以及从x或z到0同样,@negedge则在从1到xz或0,以及。

上一篇: 包含皇帝成长计划2打仗攻略的词条

下一篇: 搭建微信小程序,搭建微信小程序后端

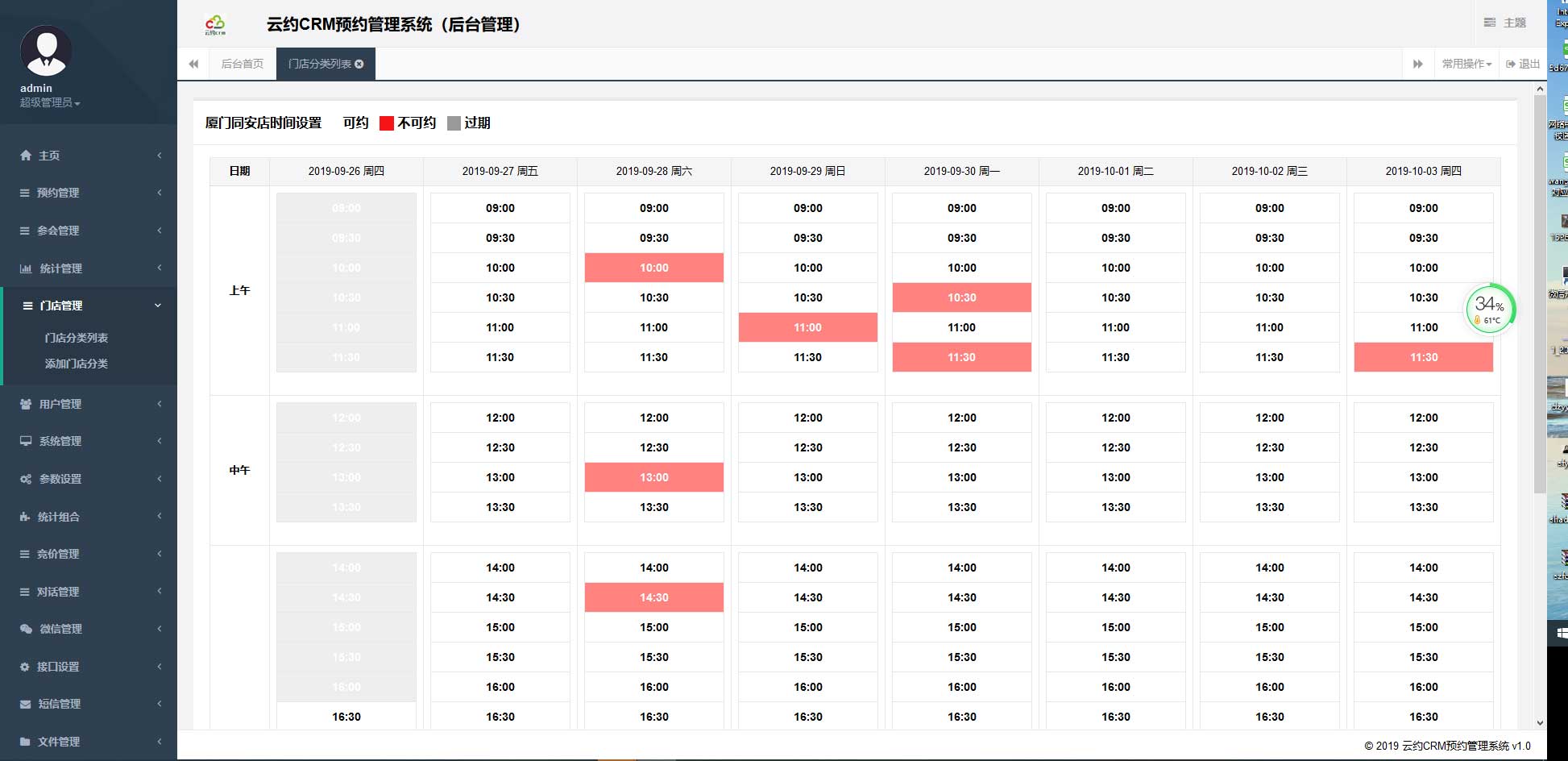

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

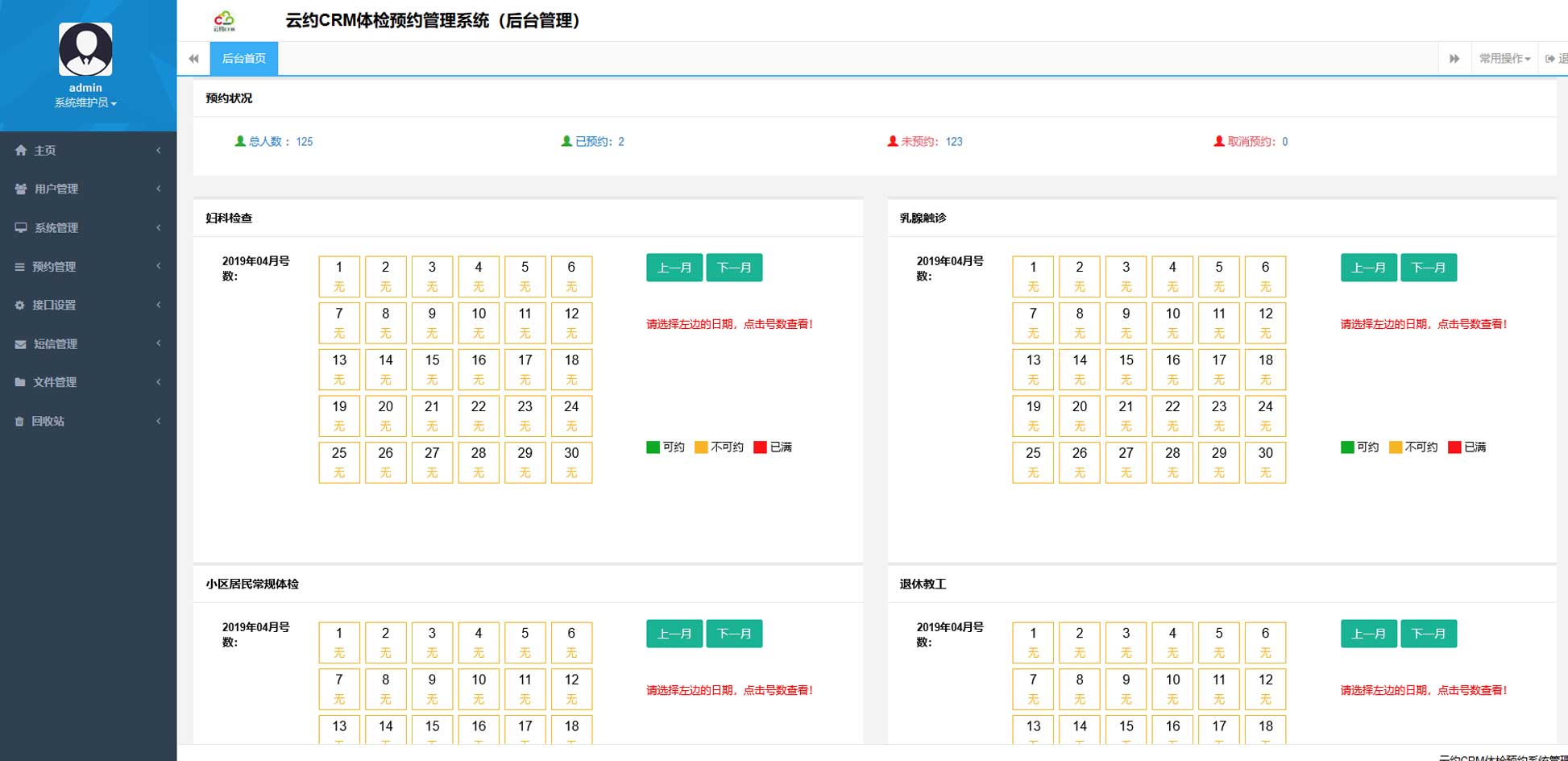

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com