PCI Express体系结构入门是一本详尽阐述PCI和PCI Express总线基础知识浅谈PCIExpress体系结构(一)的指南浅谈PCIExpress体系结构(一),特别强调浅谈PCIExpress体系结构(一)了处理器体系结构在理解这两个接口中的核心作用这本书深入剖析浅谈PCIExpress体系结构(一)了处理器体系结构,这是理解和设计PCI和PCI Express总线不可或缺的基础通过研读PCI Express体系结构入门,读者不仅能掌握PCI和PCI Express总线的。

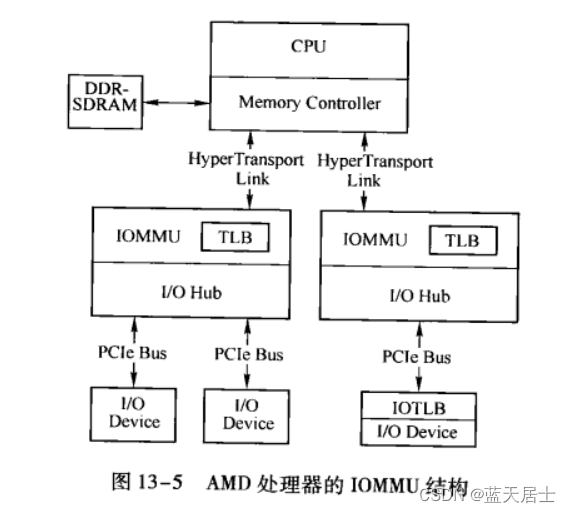

PCIe体系结构的核心组件包括Root Complex RCswitch和Endpoints EPRC类比于PCI的主桥,虽无特定规范,但在不同处理器中有不同实现,通常具备HOST主桥功能RC与switch通过FSB前端总线链接,FSB是一种传统总线,连接计算机关键组件,如CPU内存和北桥芯片RC由存储器控制器和PCI桥组成,PCI桥;PCI Express是一种高性能通用的IO互连技术,它为未来计算和通信平台提供性能和功能提升其关键属性,如使用模型负载存储架构和软件接口,继承自原有PCI技术,但其并行总线实现被高度可扩展的完全串行接口取代PCI Express利用最新技术,包括点对点互连交换机技术和分组协议,提供新的性能和功能PCI;PCI Express, 简称PCIe,其接口的位宽根据配置有所变化,包括X1X4X8和X16X2主要用于内部连接而非插槽短PCIe卡可插入长插槽,且支持热插拔,这是其显著特性PCIe支持三种电压,即+33V33Vaux和+12V,其中X16规格的接口可提供5GBs的带宽,尽管存在编码损耗,但仍能提供约4GBs的实际;主要区别1区别就是所能承受的带宽不同,也就是常说的运行速度不同但是它们之间有高到低兼容,30兼容2010,20兼容102X16表示为通道,也就是16个通道,比较多的就是1通道4通道8通道16通道通道数量越高,它的处理速度和性能越强PCI Express总线技术在当今新一代的。

在处理器系统中有几个HOST主桥,就有几颗这样的PCI总线树,而每一颗PCI总线树都与一个PCI总线域对应与HOST主桥直接连接的PCI总线通常被命名为PCI总线0考虑到在一个处理器系统中可能有多个主桥PCI总线取代了早先的ISA总线当然与在PCI总线后面出现专门用于显卡的AGP总线,与现在的PCI Express总线;PCI Express设备通过称为互连或链路的逻辑连接进行通信链路是两个PCI Express端口之间的点对点通信通道,允许它们发送和接收普通PCI请求配置,I O或存储器读写和中断INTx,MSI或MSIX 在物理层面上,一条链路由一条或多条通道组成低速外设例如80211 WiFi卡使用单通道×1;一PCI Express Capability结构 PCI Express Capability结构包含PCI Express总线相关的信息,如链路和插槽,但并非所有PCIe设备都支持此功能PCI Express Capability结构包含一系列寄存器,包括PCI Express CapabilityDevice CapabilityDevice ControlDevice StatusLink CapabilityLink ControlLink Status。

PCI Express,作为第三代高性能IO总线,其核心变革在于从并行总线转向串行总线,以及采用点对点连接方式在并行总线结构中,总线由桥接设备连接的设备组成,而在PCIe中,每条链路包含一条或多条通路,每条通路由两对差分信号线组成,没有专门的数据地址控制和时钟线,通过数据包进行传输点对点连接;PCI Express也有多种规格,从PCI Express x1到PCI Express x32,能满足将来一定时间内出现的低速设备和高速设备的需求PCIExpress的接口是PCIe 30接口,其比特率为8Gbps,约为上一代产品带宽的两倍,并且包含发射器和接收器均衡PLL改善以及时钟数据恢复等一系列重要的新功能,用以改善数据传输和数据;PCIe总线的拓扑结构通常由RC根复合体端点设备IO设备Switch交换机和PCI Express到PCIPCIX桥构成,这些组件通过PCI Express总线连接RC负责集成了PCIe总线端口存储器控制器等设备接口Switch用于扩展链路,连接多个设备,包括一个上游端口和2n个下游端口在Switch中,与RC直接或间接;为了进一步提高数据传输速度,PCIe 30标准将数据传输速率提高到了8 Gbps双向,而PCIe 40标准则将这一速率提升到了16 Gbps双向这些高速率使得PCIe成为了现代计算机架构中不可或缺的一部分总之,PCI Express作为一种高效的总线标准,通过整合所有IT,将所有组件连接到分布式背板上,显著提高。

PCI Express体系结构概览本文档详细介绍了PCI Express PCIe 体系结构的各个方面,包括PCI总线的基本知识桥与配置数据交换PCIe扩展以及与Linux系统的交互等第1章 PCI总线基础11 PCI总线结构,包括HOST主桥PCI设备信号定义等12 PCI总线的存储器读写事务,时序和传输方式13 中断;首先是PCIe架构的核心组件 **Root Complex** CPU与PCIe总线的桥梁,负责CPU请求的转换和不同类型信号的处理 **Switch** 提供扇出功能,如同一个枢纽,连接多个PCIe设备,确保通信的广度和深度 **Bridge** 跨越不同总线PCIPCIXPCIe的纽带,实现设备间的连接 **PCIe Endpo。

PCI Express Technology 30Chapter 2 PCIe Architecture Overview21 节的主要内容如下PCI Express简介革新PCI Express标志着其前身并行总线的重大革新,采用串行总线设计双向连接允许同时进行信息的发送与接收,采用双单工连接模型链路与通道用于描述设备之间信号传输路径的术语为“链路”。

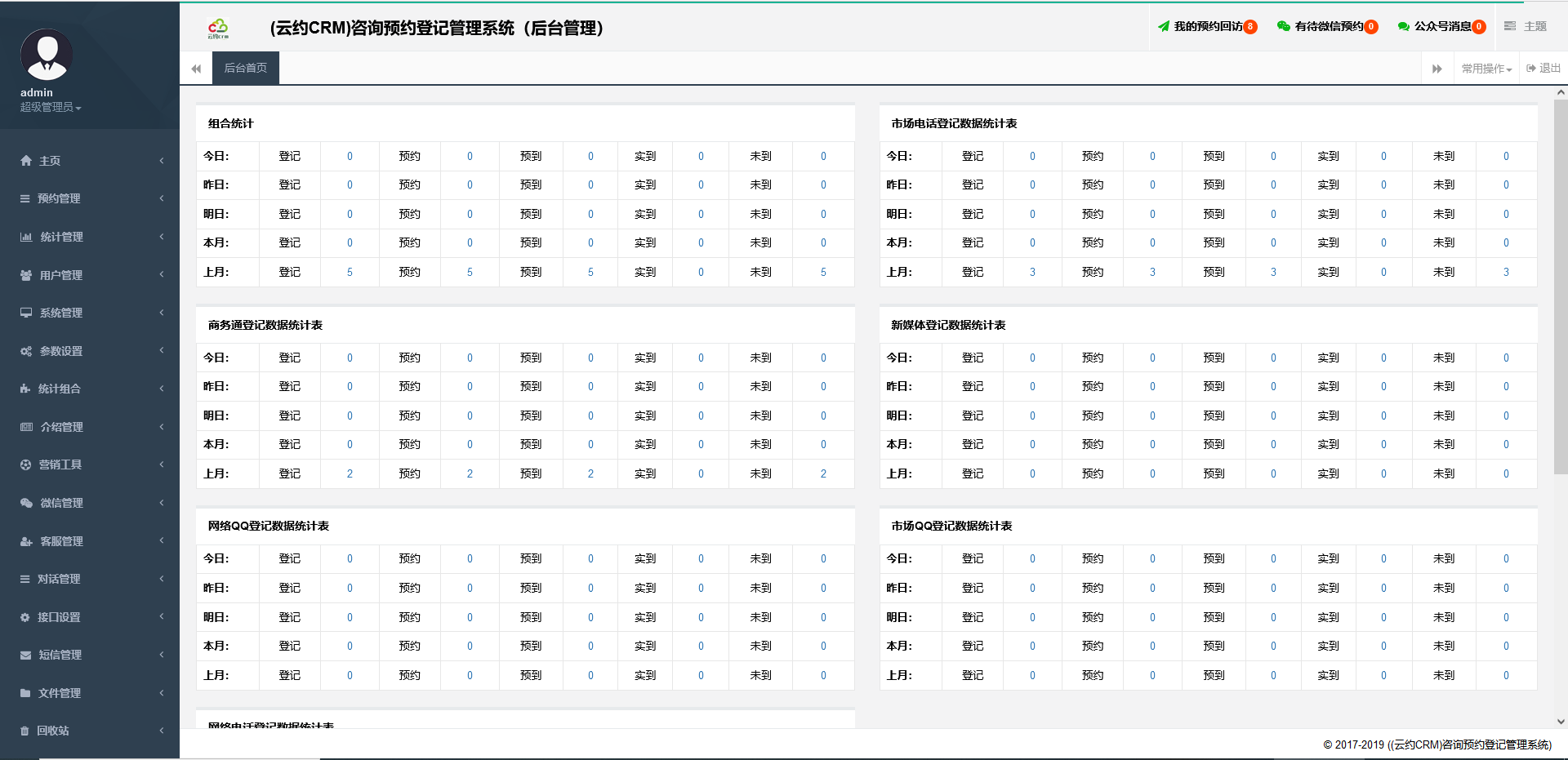

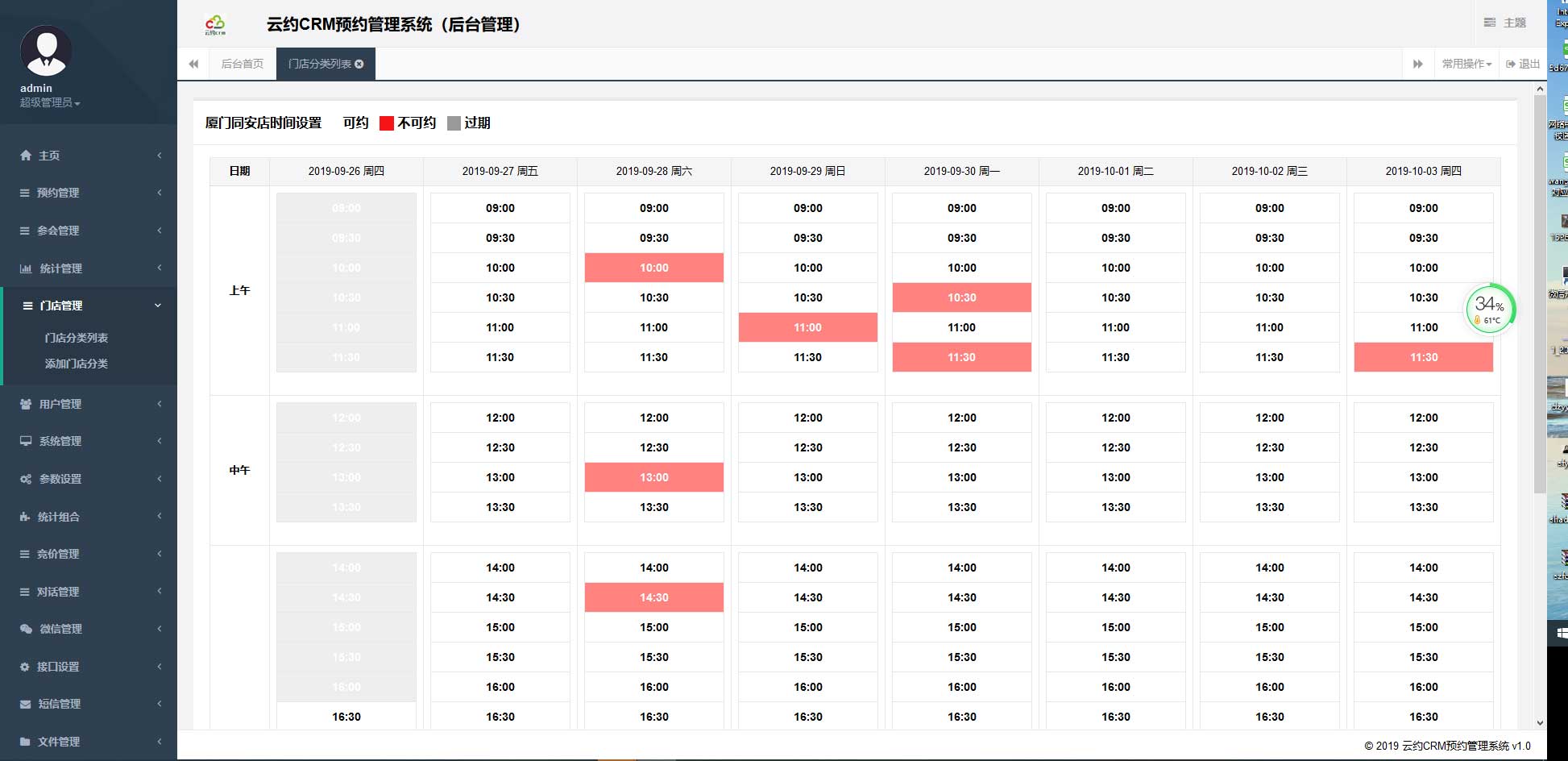

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

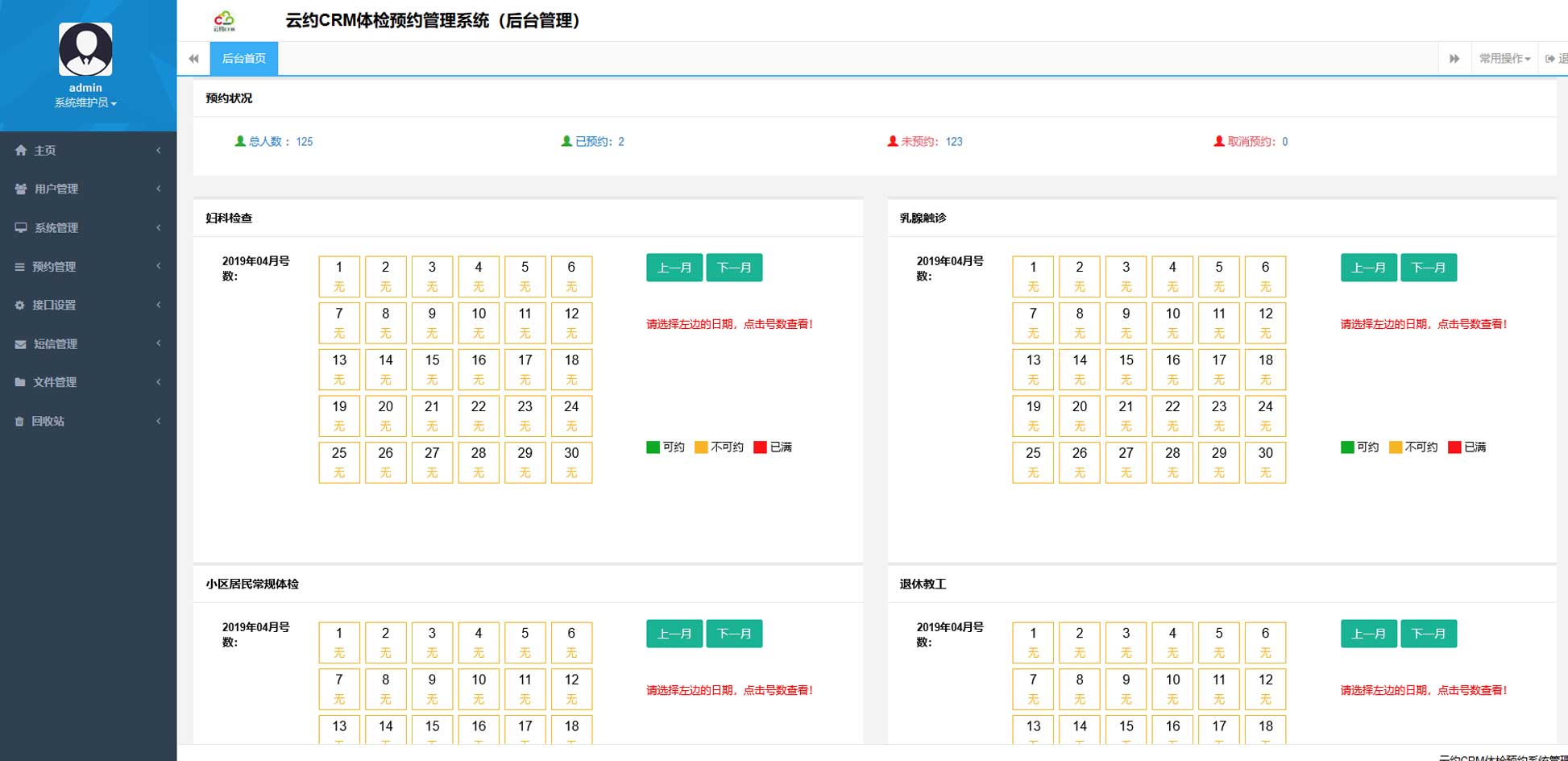

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com