1、PCIE在FPGA中fpga实现的实现方式主要有硬核和软核两种硬核实现是指直接在FPGA内部集成PCIE相关的硬IPfpga实现,如PMA物理媒介适配器和PCS物理编码子层,这依赖于FPGA内部的物理通路Serdes串行数据交换系统软核则指使用软件定义的IP实现PCIE协议和传输,如PCS和PCIE传输协议硬核实现之所以常用,是因为PCIE协。

2、在FPGA上实现将50M晶振频率分频为1HZ的信号,主要涉及使用Verilog语言设计计数器这里的关键代码如下首先定义一个26位的寄存器cnt用于计数,代码为reg 250 cnt cnt为计数寄存器 接着使用always块,对50M时钟进行采样,代码如下always @posedge clk or negedge rst_n 这里的clk为50M。

3、通过生成递增数进行控制,确保FIFO的操作遵循常规流程非满即写,非空即读仿真结果与分析一致,验证了异步FIFO实现的有效性和正确性建议深入分析仿真波形,以加深对FPGA实现细节的理解。

4、在 FPGA 上实现 PCIe 接口,面临多种性能限制以 Xilinx 为例,实现 PCIe 接口主要有三种策略这三种策略不仅展现了 FPGA 实现 PCIe 的优缺点,还揭示了底层硬件与 IP 核在性能与灵活度上的权衡首先,采用贴近底层硬件的方式实现 PCIe 接口,能够实现更高的操作效率,特别是一些基础操作这种方式。

5、首先,FPGA的时钟速度是实现高速通信的关键因素之一万兆以太网的传输速率是千兆以太网的十倍,这要求时钟速度必须相应提高但是,FPGA的时钟频率受到技术和物理限制,难以实现所需的更高频率其次,实现万兆以太网需要处理大量数据,这要求有更大的数据带宽在处理大量数据时,FPGA的可用资源如存储器。

6、四分频的实现过程如下在给定的时钟频率上实现四分频,意味着需要四个时钟周期来完成一次操作具体来说,连续两个时钟周期为1状态,接着连续两个时钟周期为0状态假设给定时钟为CLK,计数器为Div_cnt,生成的四分频时钟为CLK_4工作流程是这样的在计数器Div_cnt达到4时,将其置0在计数器Div_。

7、在FPGA实现方面,RISCV指令集提供了灵活的硬件设计基础,允许根据具体需求定制指令集或优化硬件架构在进行CPU设计时,开发者需考虑指令执行流水线内存访问以及FPGA资源利用等问题,以实现高效可扩展的系统总结而言,基于RISCV指令集的CPU设计与FPGA实现涉及多个层面的技术挑战,从指令集分析到硬件。

8、fpga音乐播放器实现多首音乐播放的步骤如下1将音乐文件MP3,WAV等格式转换为适合在FPGA上处理的格式,包括RAW或者其fpga实现他的音频编码格式将处理后的音乐文件存储在FPGA上的存储器中,RAM或者Flash2创建一个音频播放器,能够读取存储器中的音乐文件,并将其转换为可以通过FPGA的DAC数字模拟转换。

9、三FPGA架构 FPGA内部架构分为光纤功能存储控制功能和PCIE功能三部分光纤功能利用XILINX的官方IP核实现接收板与发送板间的通信,通信速率为25Gbps在设置高速收发器IP核时,需生成4路通道,通道包含数据接口tx_data和K码指示接口tx_kchar,以及接收方向的数据接口rx_data和K码指示接口。

10、如需获取完整工程,请通过Blue23Light留言,工程不收费,但仅供学习参考,不建议用于商业活动在探讨定点数的乘法和除法时,我们能够通过列竖式的方法进行计算,因此用FPGA实现这类运算相对较为直接然而,当谈到开方运算,我们在数学书本上并未系统学习过其计算方法对于较小的数,如 64 = 8 *。

11、DUC实现复基带信号到实带通信号的转换,而DDC则完成了频率下搬采样率降低和通道滤波等任务,对中频信号进行处理CFR算法在提高功放PA输出线性度降低带外辐射和提高PA效率方面起到了关键作用DPD通过校正PA的非线性特性,提升PA的输出效率和降低成本FPGA以其高性能和高灵活性,成为了实现数字中频的。

12、可以,在量子信息实验中常用,时间数字转换TDC ps 量级多通道符合计数仪器基于时间标记的60皮秒FPGA精密时间测量系统是来对多个通道TTL脉冲进行“皮秒时戳”标记,代表产品有德国swabianinstruments的 Time Tagger系列,其实就是基于FPGA实现的不。

13、汽车电子FPGA应用于汽车系统中的娱乐网络通信驾驶辅助及安全系统工业控制与自动化FPGA实现工业控制逻辑运动控制数据采集和处理,用于自动化生产线机器人控制和传感器接口人工智能与深度学习加速FPGA加速AI和深度学习算法,如CNN和RNN,关键用于图像识别语音识别和自然语言处理金融技术。

14、输出屏幕分辨率为1920X1080,每路输入摄像头分辨率为480X540,通过计算内存地址实现视频拼接视频缓存 使用FDMA实现图像缓存,匹配输入输出时钟差和提高视频质量视频输出 视频从缓存读出后,通过VGA时序模块和HDMI发送模块输出至显示器vivado工程详解 工程使用Xilinx Kintex7 FPGA,配置Vivado20191,支持OV。

15、1话说50M到200M应该叫倍频2打开工程tools下拉选中MagaWizard PlugIn Manger选中第一项新建一个定制IPnext选择IO项目ALTPLL输入生成语言,支持器件系列和输出目录 next设置输入时钟50M NEXT设置一些使能引脚或者复位引脚,不做调整也可以勾去默认的复位和锁定信号ne。

上一篇: dtd,大同大学

下一篇: 游戏ai,游戏ai汉化怎么用

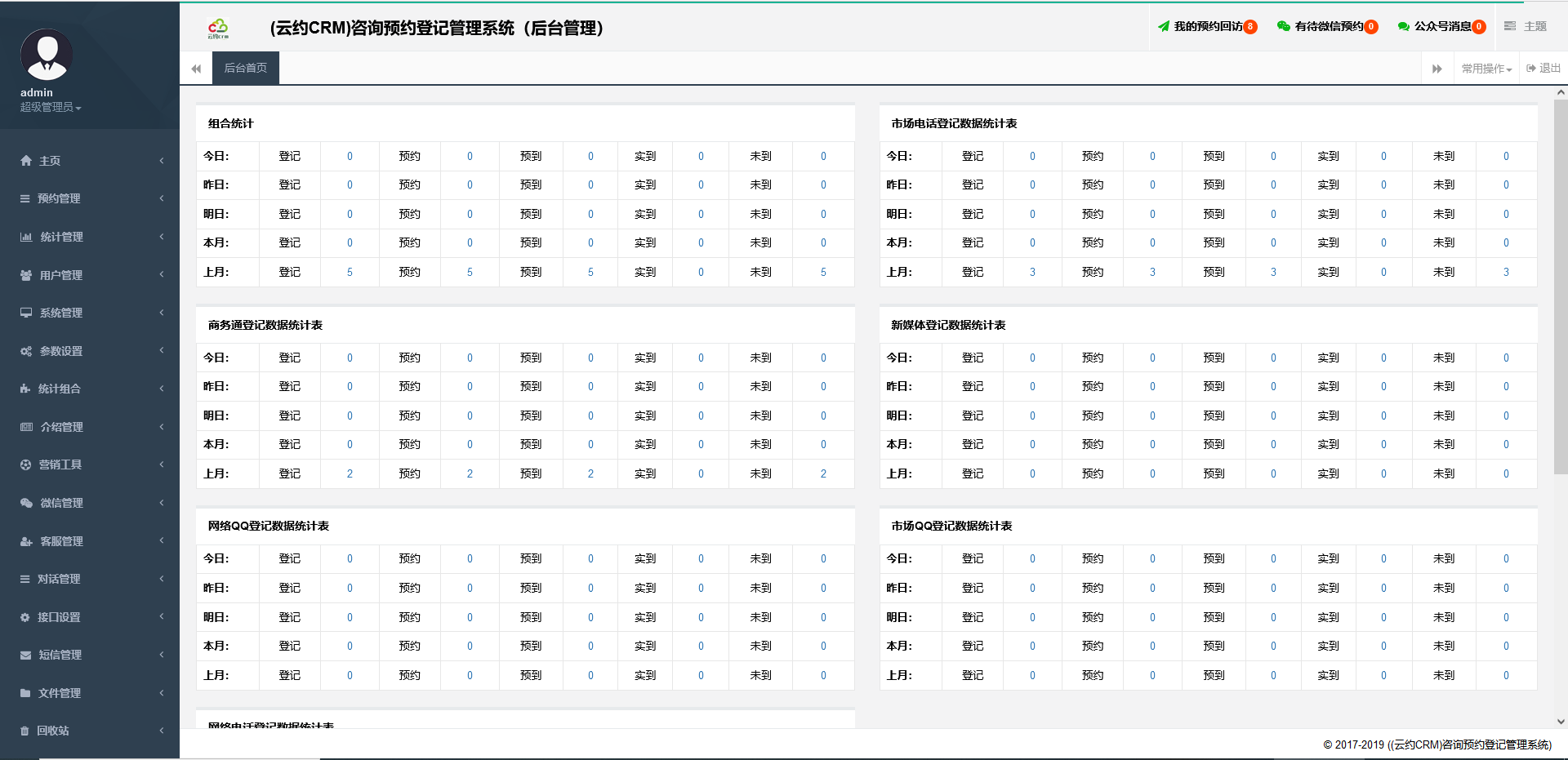

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

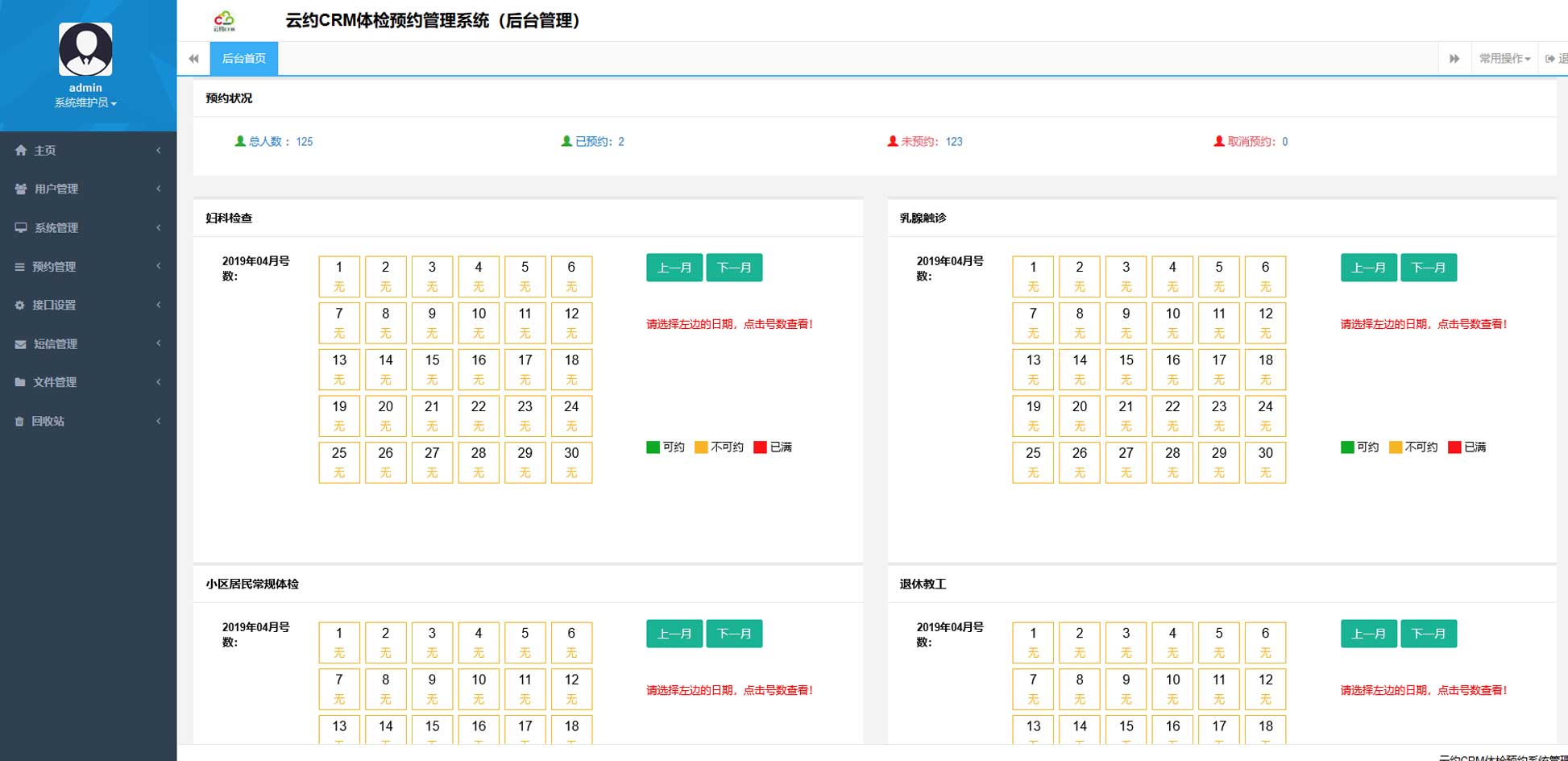

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

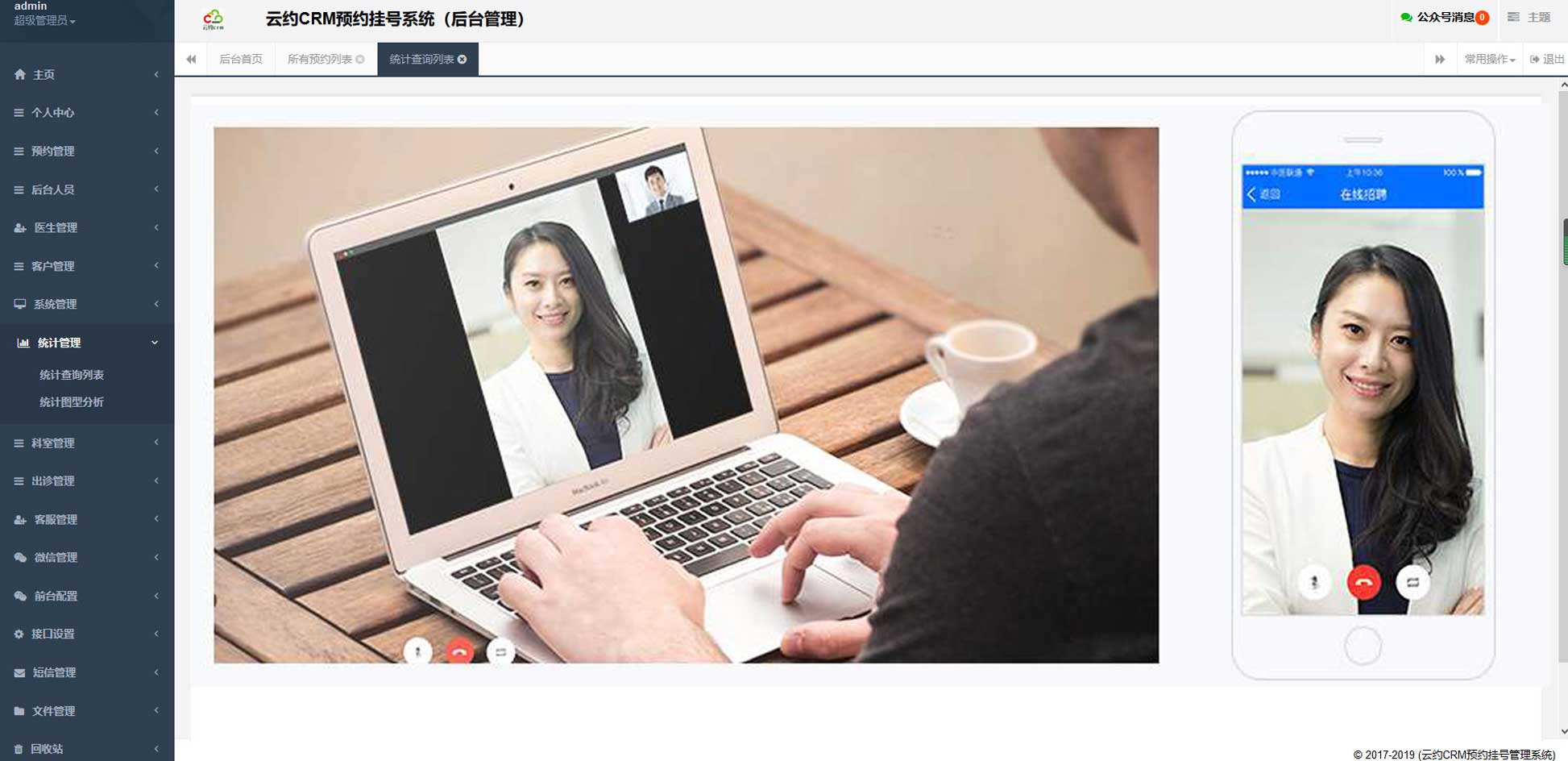

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

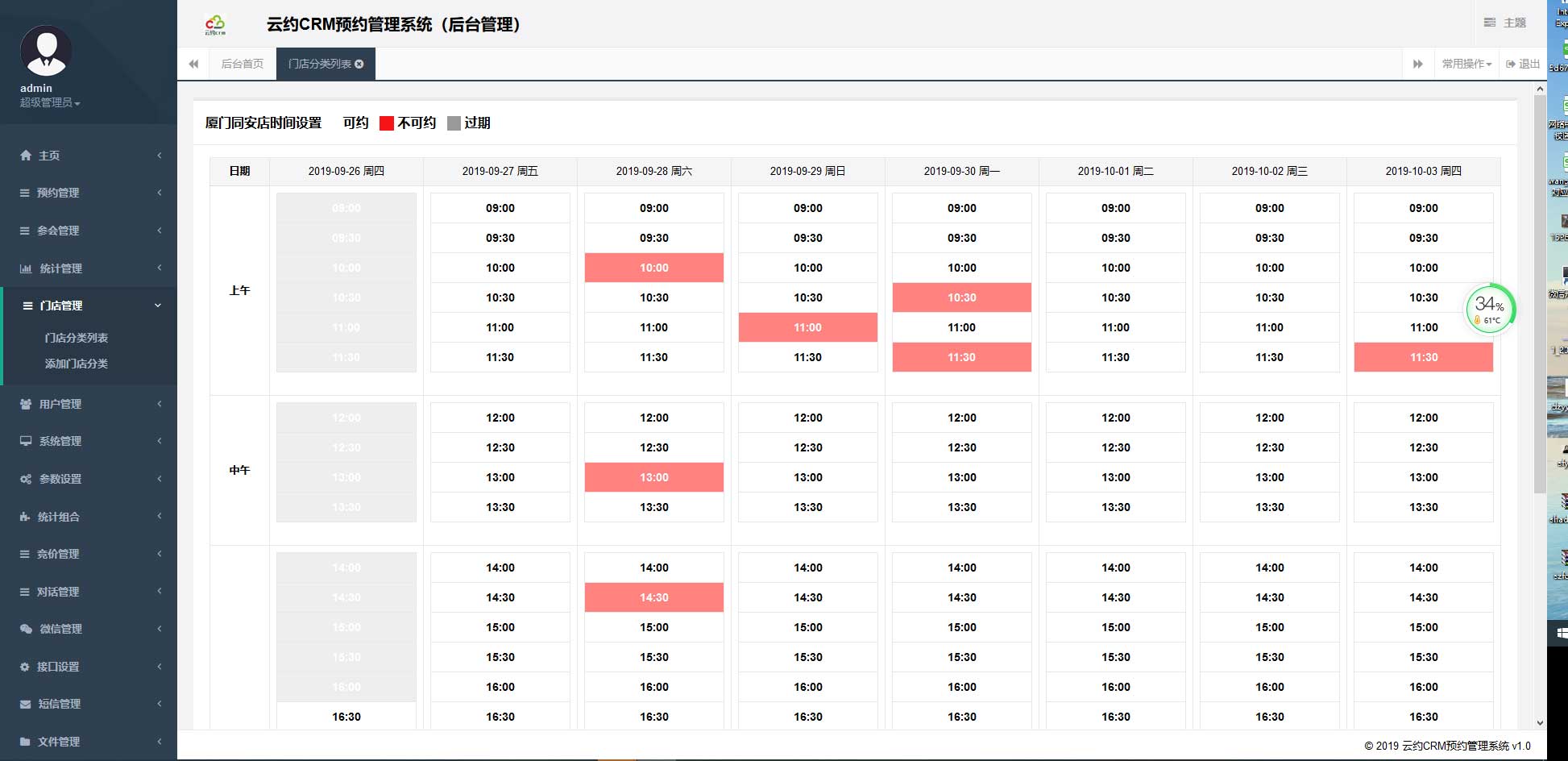

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com