1、CML电平标准 定义CML电平标准是高速串行通信中常用的差分信号电平标准cml电平标准,广泛应用于吉比特SERDES设计中cml电平标准,如Xilinx的GTXH系列等 特性CML电平标准具有可选的交流或直流终端和输出驱动,以及可选的内置线路均衡和或内部端接,非常适合吉比特链路 应用在FPGA的Transceiver或Serdes设计中,CML电平标准。

2、在高速链路中,CML电平标准作为首选,广泛应用于Transceiver技术中Xilinx的GTXH等众多协议均采用CML标准,发送与接收差分信号线以此为基准CML标准具有交流或直流终端,可选输出驱动和内置线路均衡等优势在Xilinx的管脚约束页面中,Transceiver的TXPTXN与RXPRXN引脚的电平标准虽未开放选择,实则固定,具。

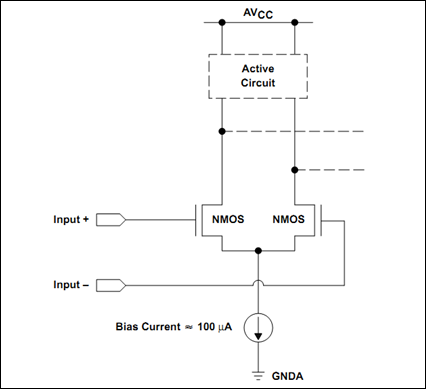

3、标准有TIAEIA644和IEEE 15963 信号特点正负电极信号差模电压摆幅为350mV,共模电压在12V左右,利用差分传输降低电磁辐射 设计考虑需考虑阻抗匹配,以确保信号完整性CML电平设计基础 定义CML,即电流模式逻辑,是一种简单且无需外部端接的高速接口,基于电流驱动,适用于高速SerDes链路。

4、LVPECL电平模式基于ECL逻辑,采用差分结构和射极输出电阻,提供强大的驱动能力VCC取值为33V或25V,VBB为内部参考电平当V1电平高于VBB时输出逻辑“1”,低于VBB时输出逻辑“0”LVPECL电平模式的功耗较大,且输入输出电平尚未形成国际标准CML电平模式常用于10Gbps以太网连接和10G XFI接口输出结构。

5、CML的单端输出可达04V,差分输出为800mVCML电平分析强调终端并联匹配,以确保50Ω单端和100Ω差分阻抗的一致性然而,CML没有统一的标准,供应商的规范各异,因此在使用时务必参照芯片手册进行精确匹配CML逻辑电平具有独特魅力速度超过CMOSLVDS,开关噪声低,理论速度可达10Gbits以上,同时低功耗。

6、pcml是一个用于超高速接口的微分标准 pcml在输入缓冲区两者之间的需要33V的 ccio和100 的终端电阻此外,每个输入痕量需要50 电阻至V TT,每个输出的痕量需要1 00 电阻至V TT要求不必输入参考电压PCML is a differential standard used for highspeed interfacing。

7、现在常用的电平标准有TTLCMOSLVTTLLVCMOSECLPECLLVPECLRS232RS485等,还有一些速度比较高的LVDSGTLPGTLCMLHSTLSSTL等下面简单介绍一下各自的供电电源电平标准以及使用注意事项TTLTransistorTransistor Logic 三极管结构Vcc5VVOH=24VVOL=2VVILlt=08V因。

8、11 PECL接口的独到之处PECL的输出结构如图1所示,包含一对差分信号和射随器,保证高速切换标准负载为50欧姆,静态电平约13V然而,低阻抗带来的优势也带来挑战,传输线的失配可能导致信号波形振铃PECL的输入结构则需要高阻抗差分对,如MAXIM的MAX3867,提供灵活的偏置选项,见图2和表一中的详细。

9、JESD204B协议是专为ADCDAC设计的传输接口标准,它包含物理层链路层传输层应用层四层物理层规定cml电平标准了使用SERDES接口和CML电平标准,链路层负责数据组帧编码及链路初始化,传输层通过链路将ADC数据以半字节单位传输,应用层则解析ADC数据供用户使用与TTLCMOSLVDS等接口标准相比,JESD204B不仅。

10、输出低电平门限低电平的界限,确保逻辑门输出稳定阈值电平虽然表示电路动作的临界点,但实际设计中,Vih和Vil更为关键输出电流衡量高电平和低电平时的驱动能力输入电流反映输入信号对电路的影响逻辑电平的多样性和应用存在多种逻辑电平标准,如TTLCMOSECLPECLLVDSLVPECL等,各有。

11、引脚定义在设计系统时,需深入理解SFP+光模块的引脚定义,如SFF8431型号的光模块,其电气接口SFI是ASIC芯片和模块间的连接通道阻抗匹配电气接口SFI的标称差分阻抗为100ohm,在PCB布局时需遵循特定的微带线或带状线推荐参数电平标准与速率控制电平标准需注意LVTTL和CML电平标准速率控制如RS01。

12、GTLGated Transistor LogicPGTLPushPull Gated Transistor LogicCMLCurrent Mode Logic等,由于其高速度和低噪声特性,常用于高速数据总线和高速接口设计最后,HSTLHighSpeed TTLSSTLSemiSynchronous TTL等是针对更高速度和更严格的信号质量控制设计的高级电平标准。

13、CML 电平对接的必须也是SERDES,一般有交流耦合和直流耦合板内走线短可以直流耦合,走线长推荐交流耦合。

14、每个电平标准都有其独特的参数,如LVPECLLVDS和CML,它们的输入和输出门限参数通常保持一致,这是由差分信号的设计结构所决定的,旨在提供更高效和可靠的信号传输为了确保最佳性能,始终建议查阅特定芯片的datasheet,以获取最准确的电平参数和使用指南在这个不断发展的电子世界中,理解信号逻辑电平的演变。

15、深入了解JESD204BADCDAC传输协议的高速王者 JESD204B,这个专为高速ADCDAC数据传输而生的标准,以其独特的架构和性能优势,引领了接口技术的革新它涵盖了物理层的SERDES CML电平标准,以及链路层的8B10B编码与并行数据帧设计相比于TTLCMOS和LVDS等传统电平标准,JESD204B提供了精确的时序规。

上一篇: 深入Android源码系列(一)开发者社区,安卓开源代码库

下一篇: 智慧景区管理系统,智慧景区管理系统物联网

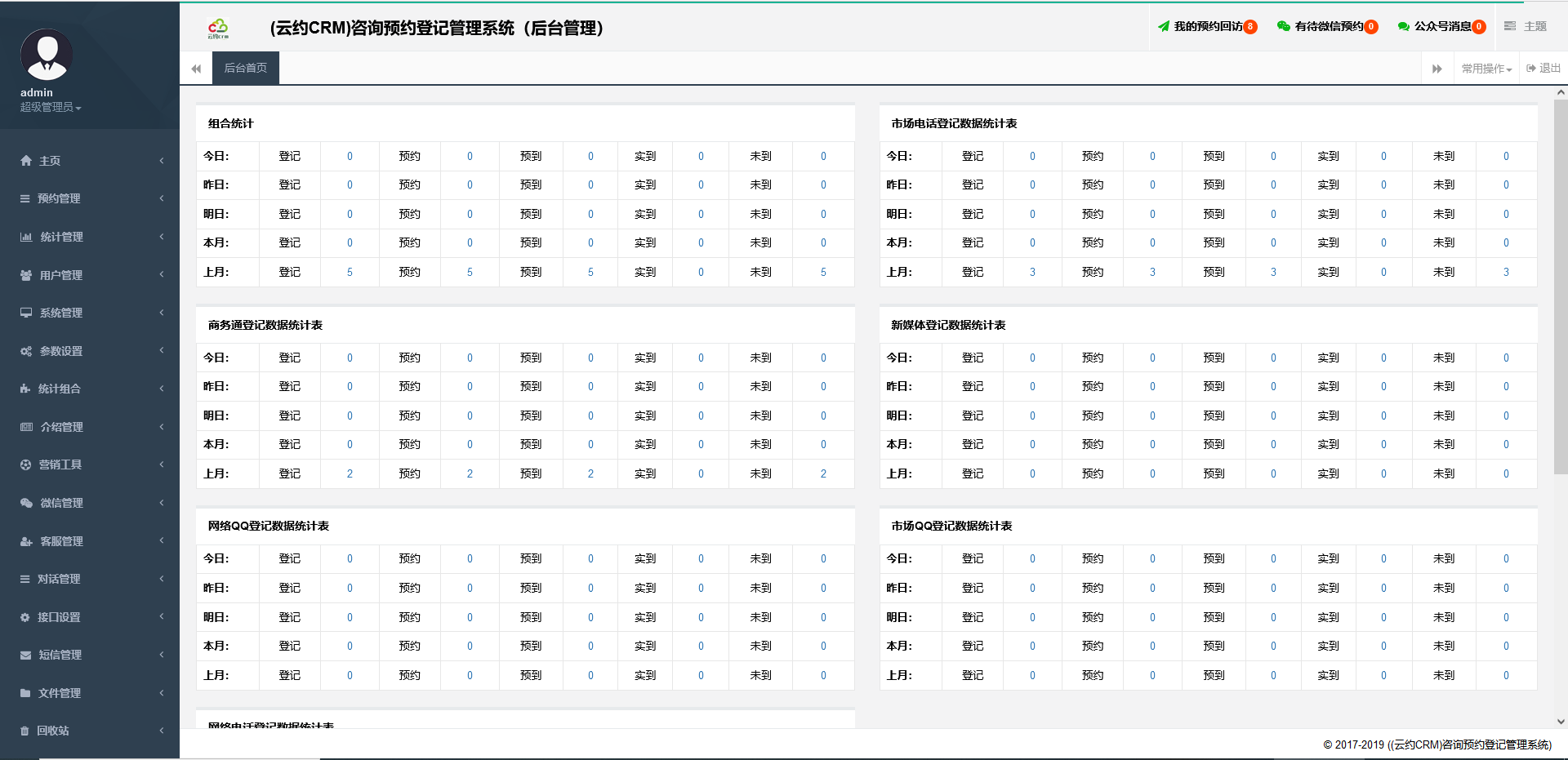

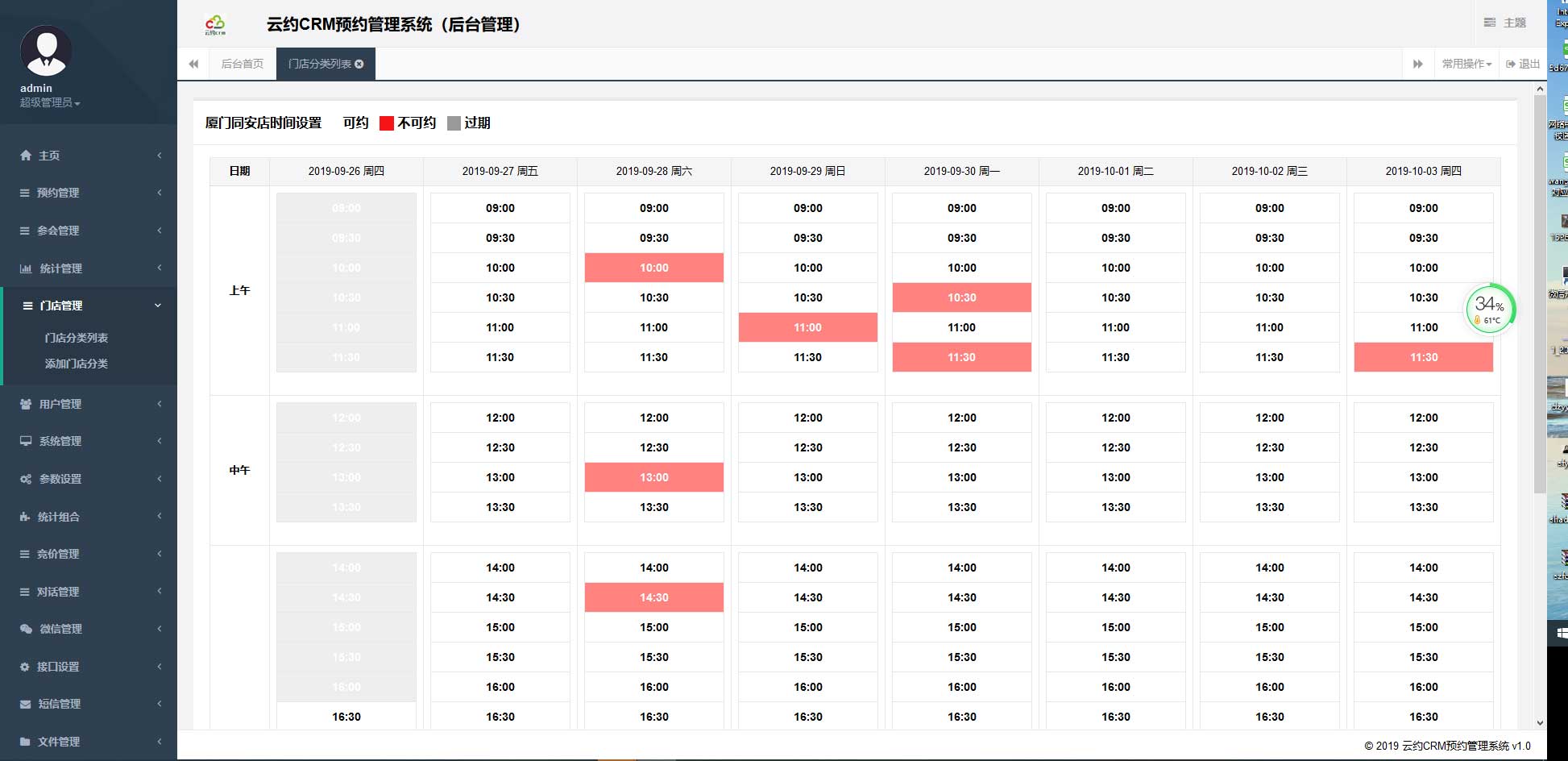

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

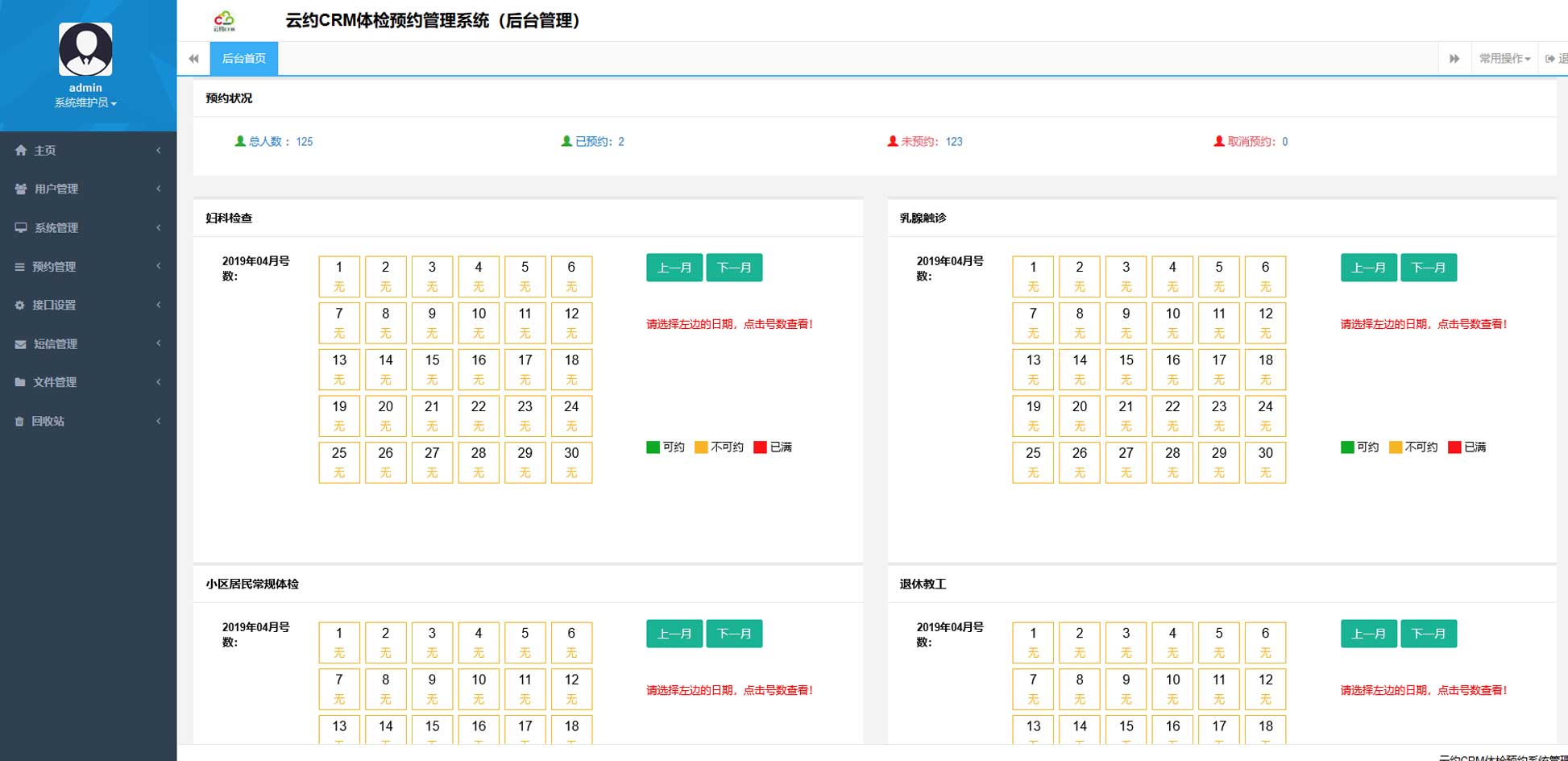

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

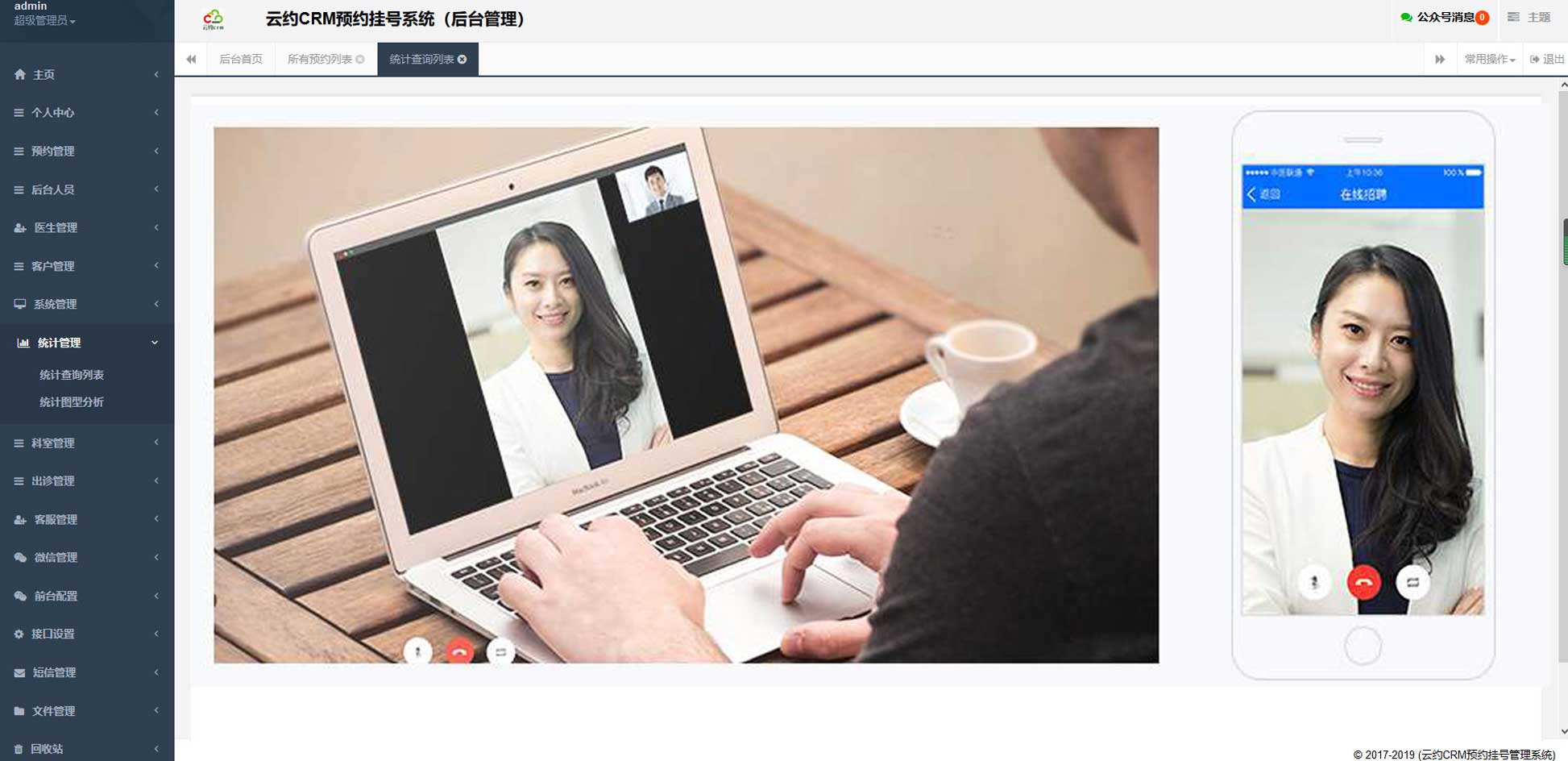

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com