1 项目核心 纯verilog实现不依赖任何IP核fpga项目,如FIFO或RAMfpga项目,保证fpga项目了高度的移植性和灵活性 10GUDP高速协议栈提供高速UDP通信的解决方案,适用于高端FPGA项目2 工程源码 7套完整源码覆盖了多种速率和接口类型,从1G到10G,甚至25G,确保广泛适用性 针对Xilinx vivado专为Xilinx系列FPGA器fpga项目;在开发FPGA项目时,我们常会遇到需要输出方波时钟的需求实际上,FPGA芯片上确实有固定几个脚位专门用于接收时钟输入,这在Quartus软件的Pin Assignment设置中可以很容易识别出来具体来说,在Location下拉菜单中会标注有Dedicated Clock的引脚,这样的引脚可以用来直接连接外部时钟源然而,在实际硬件开发过程;FPGA高端项目实现SDI视频编解码,提供3套工程源码与技术支持 本文详细阐述了如何使用Xilinx Kintex7325T FPGA开发板进行SDI视频编解码,设计过程涵盖了从输入高清SDI信号,通过GTX解串SMPTE SDI解码,到最终输出HDMI或SDI视频的全过程三种不同的工程源码分别对应不同的输出模式HDMI输出工程1。

工程提供两套vivado20222版本的FPGA源码,一套支持1路SDI摄像头回环,另一套支持4路摄像头回环注意本工程专为Xilinx UltraScale和UltraScale+系列FPGA设计,其fpga项目他系列或型号的FPGA不支持UltraScale GTH IP核提供完整工程源码和技术支持,适用于学生研究生项目在职工程师学习提升,以及医疗军工等;直流电机伺服控制系统 1 任务 使用FPGA为核心器件设计并制作一个直流电机伺服控制系统2 要求 1 基本要求1实现PWM逻辑和桥式驱动电路以驱动小型直流电机5W以下,可开环控制其转速变化2实现测速电路和逻辑,可采用光电方式,能够测量并显示电机的实时转速3实现PID反;265视频编码技术的VerilogFPGA开发者来说,复旦大学的H265 Video Encoder IP Core是一个非常好的选择,其文档详细且项目完成度高 GitHub上的开源H265项目也提供了丰富的资源和说明,适合有一定基础的开发者进行学习和实践 而对于H264项目,由于信息较少,建议在使用前进行充分的评估和测试;FPGA项目 Hummingbirdv2 E203 Core and SoC展示了芯来科技在RISCV领域的创新成果,适用于AIoT等领域 平头哥无剑100华为推出的RISCV平台,同样适用于AIoT等领域,展示了华为在该领域的创新实力 FPGA资源整合项目该项目整合了FPGA相关的网站工具教学视频和开源项目,为FPGA应用提供了一站式;GitHub上提供了丰富多样的Verilog和FPGA项目,适合不同阶段的学习者例如,#39HDL Bits Solution#39为学习者提供了参考答案,加速理解过程对于RISCV处理器设计感兴趣的开发者,#39香山开源高性能处理器#39展现了中国科研实力,其架构设计和流片计划为研究提供了宝贵资源#39木心处理器#39在集成开发环境和教程方面;本项目旨在实现SDI视频的接收与发送,并在接收视频流上叠加动态字符项目基于GS2971接收器和GS2972发送器,利用Xilinx系列FPGA的GTPGTX资源解串和SMPTE SDI资源进行编解码本文详细介绍了硬件实现方案和软件支持项目硬件部分采用Xilinx的Zynq7100xc7z100ffg9002中端FPGA开发板,利用GS2971接收同轴SDI;FPGA高端项目6GSDI 视频编解码,提供工程源码和技术支持 前言Xilinx系列FPGA实现SDI视频编解码的方案主要有两种一是使用专用编解码芯片,如GS2971和GS2972,优点是简单,但成本较高二是使用FPGA实现,通过合理利用FPGA资源实现解串,操作难度稍大,对FPGA水平要求较高UltraScale GTH适用于Xilinx。

在FPGA板上运行将“src”文件夹中的源文件添加到您的FPGA项目中顶部文件是decode_streamsv两个接口,stream_mem_xxx用于将H265比特流馈送到解码器github上的开源H264,开源地址githubcomaiminickwong无介绍 说明第一个项目由复旦大学专用集成电路与系统国家重点实验室State Key;这是一个基于Xilinx Zynq UltraScale+MPSoCs型号FPGA的高端项目,实现了UltraScale GTH + SDI 视频编解码以及SDI无缓存回环输出,并提供2套工程源码和技术支持具体要点如下实现方式使用Xilinx Zynq UltraScale+MPSoCs型号FPGA结合UltraScale GTH IP核和SMPTE UHDSDI IP核进行SDI视频编解码通过LMH;FPGA高端项目纯verilog的 25GUDP 高速协议栈,提供工程源码和技术支持 前言在现有的FPGA实现UDP方案中,我们面临以下几种常见挑战和局限性首先,有一些方案使用verilog编写UDP收发器,但在其中使用了FIFO或RAM等IP,这种设计在实际项目中难以接受,因为它们缺乏基本的问题排查机制,例如ping功能其次。

9 hdmits模拟基于 IP 的低延迟 HDMI 视频通信系统,利用 RVSYNC 实现远程虚拟同步githubcomaomtokuhdmi10 HDMIdatastreamsSpartan6模拟+Driver将 HDMI 数据流传输到 HDMIDVI 显示器的 Spartan 6 FPGA 项目githubcomNancyChauha11 AnalogToDigital;项目概述使用Xilinx 7系列Kintex7ndashxc7k325tffg6762型号FPGA实现3GSDI视频+音频编解码功能适用于医疗军工领域或图像处理等高速接口相关应用设计部分3GSDI视频编码使用静态彩条作为源数据,通过SMPTE SDHD3GSDI IP核编码,GTX进行串化,GV8500芯片增强驱动,最终通过SDI接口输出至显示。

上一篇: 数字签名工具,数字签名工具10

下一篇: 安卓app开发,安卓app开发公司

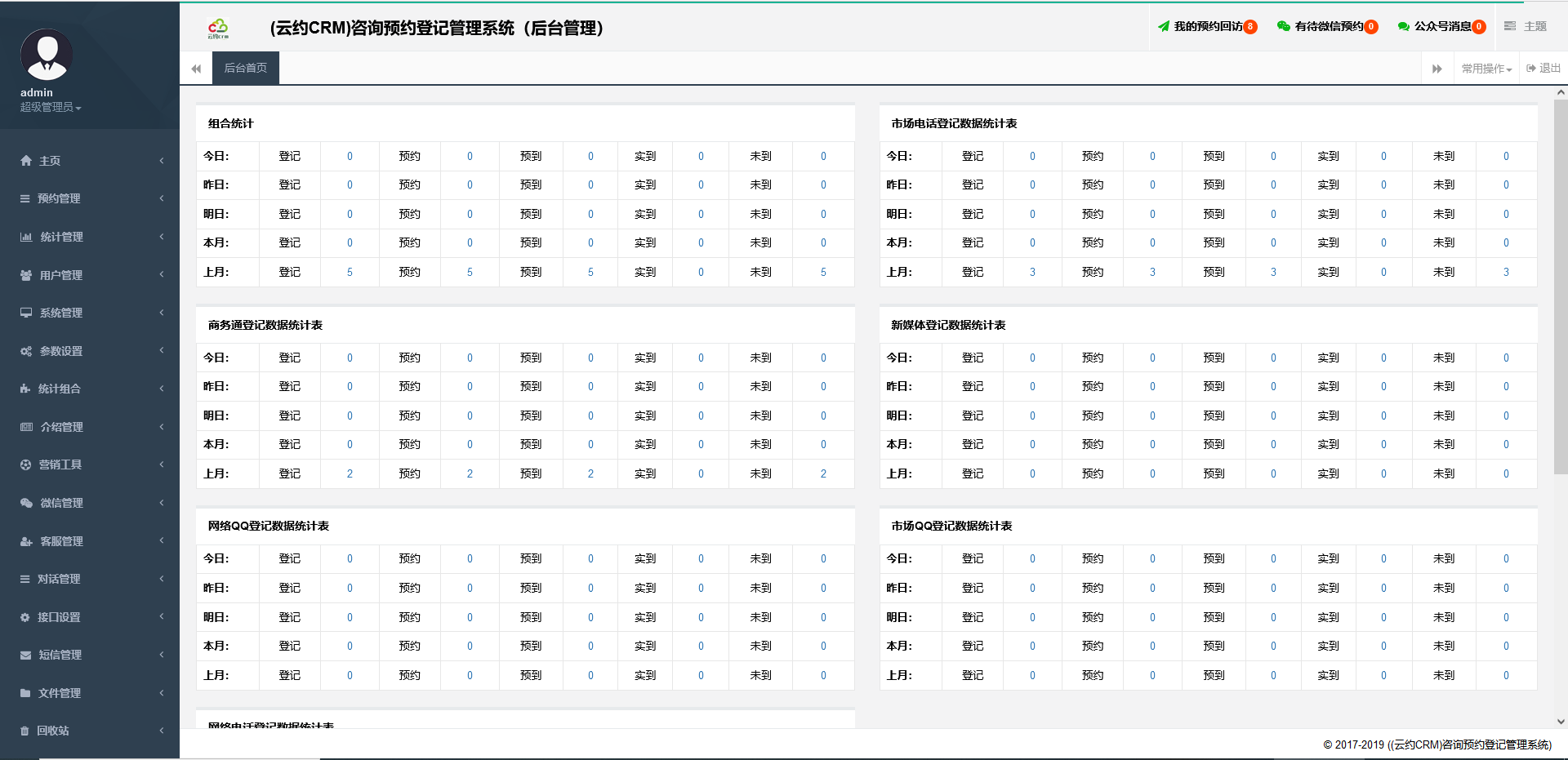

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

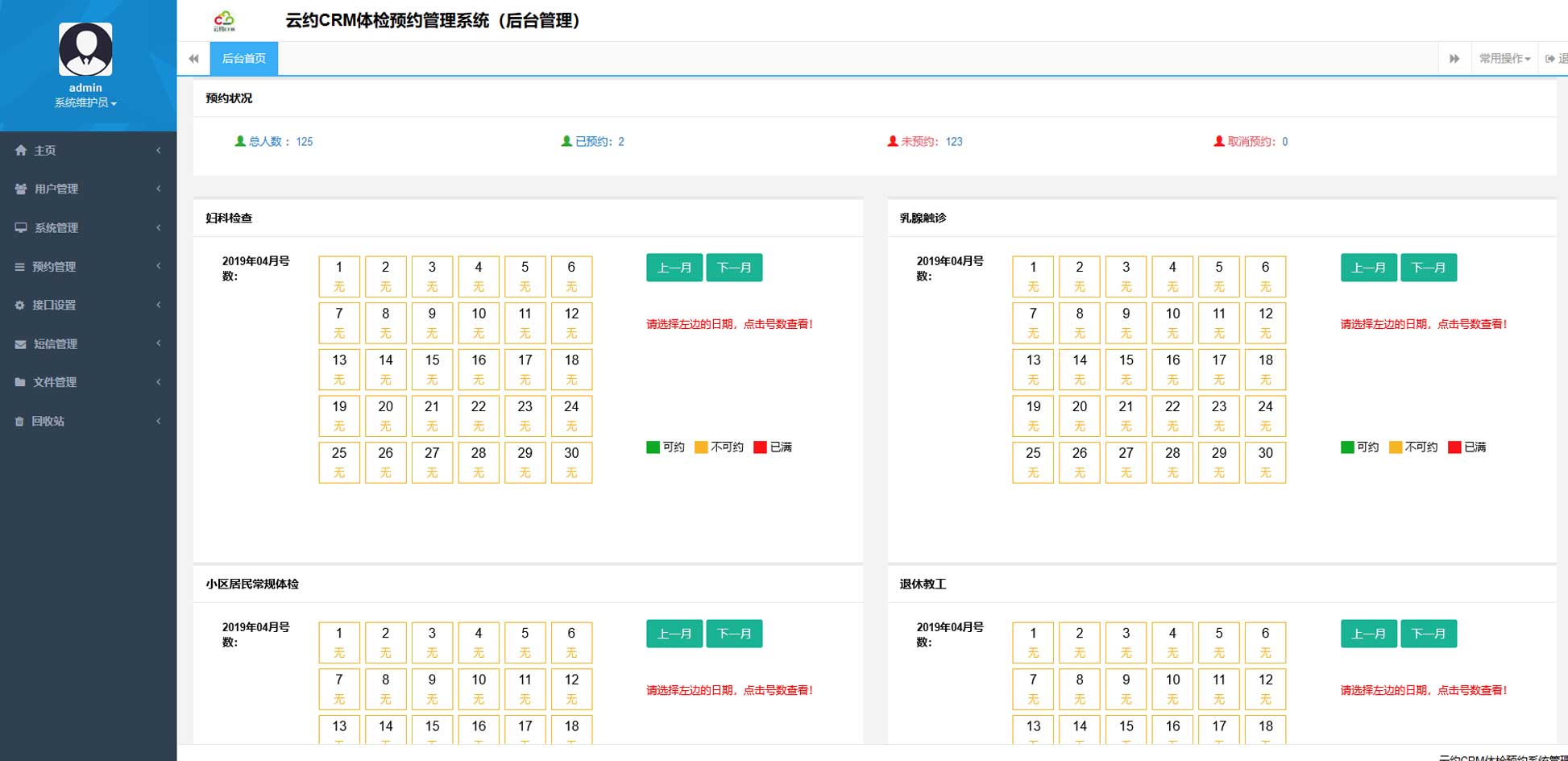

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

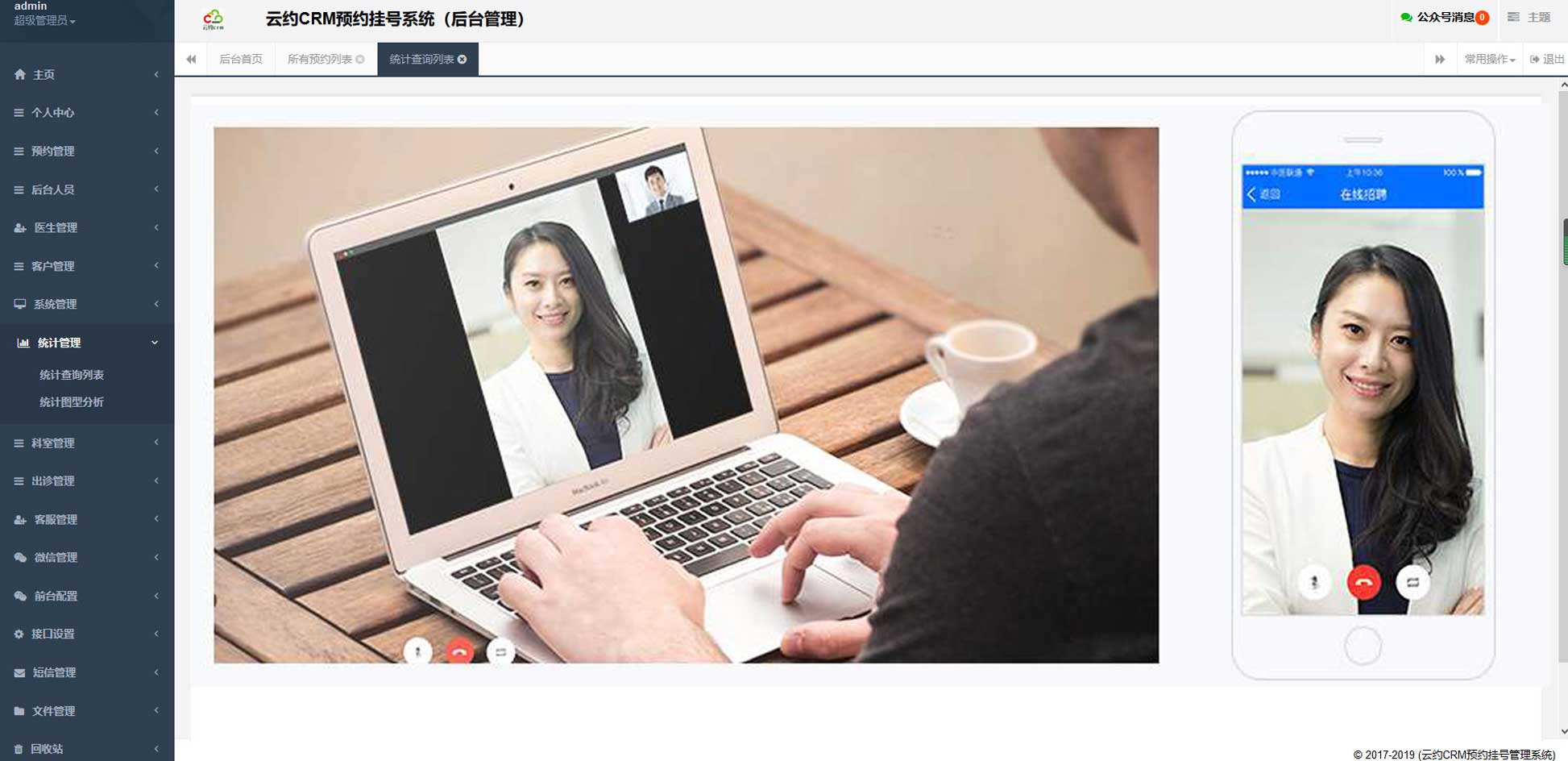

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

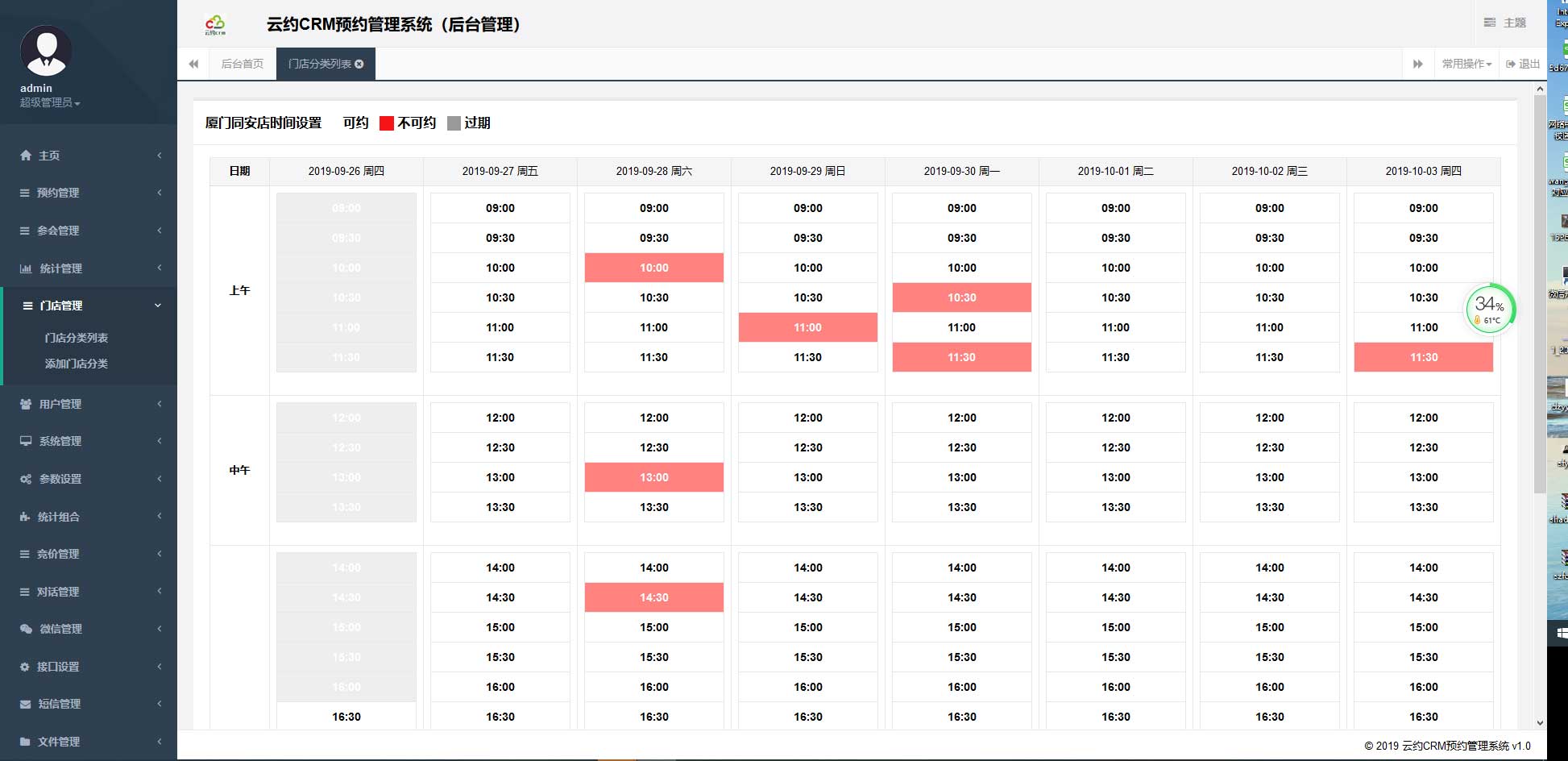

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com